# INVESTIGATION ON CASCADED H-BRIDGE FIVE-LEVEL INVERTER-BASED ACTIVE POWER FILTER

# Ph.D. Thesis

**SOUMYADEEP RAY**

(2015REE9034)

DEPARTMENT OF ELECTRICAL ENGINEERING

MALAVIYA NATIONAL INSTITUTE OF TECHNOLOGY JAIPUR

JAIPUR - 302 017 (INDIA)

JANUARY, 2019

# INVESTIGATION ON CASCADED H-BRIDGE FIVE-LEVEL INVERTER-BASED ACTIVE POWER FILTER

Submitted in

fulfillment of the requirements for the degree of

**Doctor of Philosophy**

by

Soumyadeep Ray

(2015REE9034)

*Under the supervision of*

Dr. Nitin Gupta

Prof. R. A. Gupta

DEPARTMENT OF ELECTRICAL ENGINEERING

MALAVIYA NATIONAL INSTITUTE OF TECHNOLOGY JAIPUR

JANUARY 2019

| © MALAVIYA NA | TIONAL INSTITU | TE OF TECHNOL | OGY JAIPUR-2018. |

|---------------|----------------|---------------|------------------|

|               |                | S RESERVED.   | 001 g/H 0X 2010. |

|               |                |               |                  |

|               |                |               |                  |

|               |                |               |                  |

|               |                |               |                  |

|               |                |               |                  |

**DECLARATION**

I, Soumyadeep Ray, declare that this thesis titled, "Investigation on Cascaded

H-Bridge Five-Level Inverter-Based Active Power Filter" and the work presented

in it, are my own. I confirm that:

• This work was done wholly or mainly while in candidature for a

research degree at this university.

• Where any part of this thesis has previously been submitted for a degree

or any other qualification at this university or any other institution,

this has been clearly stated.

• Where I have consulted the published work of others, this is always

clearly attributed.

• Where I have quoted from the work of others, the source is always

given. With the exception of such quotations, this thesis is entirely my

own work.

• I have acknowledged all main sources of help.

• Where the thesis is based on work done by myself, jointly with

others, I have made clear exactly what was done by others and what

I have contributed myself.

Place: Jaipur

Date:

Soumyadeep Ray

(2015REE9034)

# Department of Electrical Engineering MALAVIYA NATIONAL INSTITUTE OF TECHNOLOGY JAIPUR

#### **CERTIFICATE**

This is to certify that the thesis entitled "Investigation on Cascaded H-Bridge Five-Level Inverter-Based Active Power Filter" being submitted by Soumyadeep Ray (ID No. 2015REE9034) is a bonafide research work carried out under our supervision and guidance in fulfillment of the requirement for the award of the degree of Doctor of Philosophy in the Department of Electrical Engineering, Malaviya National Institute of Technology, Jaipur, India. The matter embodied in this thesis is original and has not been submitted to any other University or Institute for the award of any other degree.

Place: Jaipur Date:

Dr. Nitin Gupta

Assistant Professor

Department of Electrical Engineering

MNIT Jaipur

Jaipur- 302 017, India

Prof. R. A. Gupta

Professor

Department of Electrical Engineering

MNIT Jaipur

Jaipur- 302 017, India

#### **ACKNOWLEDGEMENTS**

Honestly, acknowledging contribution and support that was extended to me generously and thanklessly, is one of the most difficult, but inevitable, task. But, I would like to pen down some of them through this opportunity. This research work is an outcome of true moral support from individuals/group members directly or indirectly involved with me during my research work at Malaviya National Institute of Technology Jaipur.

I, from the bottom of my heart, want to express sincere acknowledgement with warm regards and gratitude to my thesis supervisor **Dr. Nitin Gupta**, Assistant Professor, Department of Electrical Engineering, Malaviya National Institute of Technology Jaipur for his proficient and enthusiastic guidance, constructive criticism, encouragement and immense support throughout the research work for Ph.D. degree. He has been a constant source of inspiration for the completion of this research work. I am sincerely indebted to him for his pronounced individualities, humanistic and warm personal approach, and excellent facilities provided to me in the laboratory to carry out this research work smoothly. My great appreciation also goes to my second supervisor **Prof. (Dr.) R. A. Gupta**, Professor, Department of Electrical Engineering, Malaviya National Institute of Technology Jaipur for his precious and useful critics during the course of this research. Working under both of them has been a great privilege and to develop insight in the world of research. I humbly acknowledge a lifetime's gratitude to them.

I would like to acknowledge my research committee members **Prof.** (**Dr.**) **Harpal Tiwari, Dr. Dipti Saxena** (Associate Prof. EE Dept.), for their time to time critical examination of my research work and made constructive recommendations.

I heartily extend my gratitude to **Prof.** (**Dr.**) **Rajesh Kumar**, Professor & Head, Department of Electrical Engineering, Malaviya National Institute of Technology Jaipur for his humanistic, encouraging and warm personal approach and for the necessary facilities provided to me to carry out my research work.

I am also thankful to the whole administrative and technical staff. My special thanks to **Mr. Dhara Singh** of Electrical Machine Laboratory and **Mr. Vishnu Sharma**

of Power Electronics and Drives Laboratory, Department of Electrical Engineering for their substantial technical assistance and co-operations during my experimental work.

My sincere thanks to the **family members of my supervisors**, **Dr. Nitin Gupta** and **Prof. (Dr.) R. A. Gupta**, who have rendered immense support to them so that they would able to devote enough of their precious time for this work.

I thankfully acknowledge the precious financial support provided by **Ministry of Human Resources and Development (MHRD)**, without which it would be difficult to carry out the work at this stage. The other financial support provided by former Head of the Department, **Prof. (Dr.) Vikas Gupta**, Department of Electrical Engineering, Malaviya National Institute of Technology Jaipur is sincerely and honestly acknowledged. I am also grateful to the whole faculty members of Department of Electrical Engineering, Malaviya National Institute of Technology Jaipur for their support and motivation.

I am thankful to **Mr. Avdesh**, Design Engineer, Dynafusion Pvt. Ltd. for giving lot of help in code generation process during the experimental validation.

My heartfelt thanks to Dr. Pradeep Anjana, Mr. Ajay Kumar, Mr. Rahul Garg, Mr. Dileep Kumar, Mr. Bhatt Kunalkumar, Mr. Vijayakumar Gali and Mr. Nirav Patel who generously spent their precious time and evinced personal care and concern at every stage of this research work by sharing their research and field experiences. I will never forget the help of my good friends Dr. Manoj Kumwat, Mr. Saurabh Kumar, Mr. Prasun Sanki, Mr. Debanjan Roy, Mrs. Sushree Subhadarsini, Ms. Punyashree Pattanayak, Mr. Gaurav Khare, Mr. Mayuresh Dave, Mr. Nandikesh Pushraj, Ms. Rajveer Kaur, Mr. Jitendra Kumar Nama, Mrs. Niharika Gotherwal, Mr. Manaswi Srivastava, Mr. Pawan Singh Tomar and Mr. Subham Kumar Jalan. They always kept me motivated by their caring words and wholehearted supports and help during the research work. I wish to thanks everybody who has directly or indirectly helped me throughout my research work.

Last but not the least; I would like to express my deep gratitude to my family members for all they have undergone to bring me up to this stage. I wish to express gratitude to my parents, **Mr. Pradip Ray** and **Mrs. Tripti Ray** for their kind support, the

confidence and the love they have shown to me. My special thanks to other family members to their patience, cooperation and understanding during the course of my Ph.D. work.

At the end of my thesis, it is a pleasant task to express my thanks to all those who contributed directly or indirectly in many ways to the success of this study and made an unforgettable experience for me.

For any glitches or inadequacies that may remain in this work, the responsibility is entirely my own.

Last but not the least I would like to thank to Almighty 'GOD' for giving me health, strength and perseverance to continue till the end.

(SOUMYADEEP RAY)

#### **ABSTRACT**

Recently, power quality (PQ) is becoming an important aspect for engineers and researchers as large amount of grid integration takes place in distribution network. Medium-voltage and high-power distribution system caught every one's attention as large-scale conventional as well as renewable energy integration is taking place in current distribution system. Most of the high-power and medium-voltage equipments used by distribution sector comprises of adjustable electric drive which produces non-linearity into the existing system due to switching action of converter switches. Current harmonics generated by non-linear loads create major problem in distribution system. Current harmonics also produce voltage harmonics in combination with line impedance which propagates to distribution side consumers through point of common coupling. Many national and international regulatory standards are defined like IEEE-519-1992, IEC 61000 etc. in order to describe PQ limits.

Active power filter (APF) is a mature technology till date to counter several major PQ concerns. APF can be used for mitigating current harmonics; reactive power nullification, load current balancing with its effectiveness to solve neutral current issue. Two-level inverters are normally used as a main component of APF in low-voltage and low-power distribution system but for medium-voltage and high-power applications, multilevel inverters (MLIs) have become more attractive solution for their distinct advantages over the two-level inverters. Topology wise three fundamental types of MLIs are projected in literature namely, diode-clamped multilevel inverter, flying capacitor MLI and cascaded H-bridge MLIs (CHB-MLIs). Among these topologies, CHB-MLIs reach to higher voltage and power level due to its modular structure. In view of above theory, a through literature survey on topological aspect and various control techniques of MLI based APF has been done and a comprehensive review is presented. Among all these relevant application, CHB-MLI based SAPF is widely demonstrated in literature due to least number of device counts among all other MLIs and modularity. This topology is one of the most suitable technologies available in present medium-voltage distribution sector for reducing PQ problems. Therefore, this thesis deals with design and

development of CHB-MLI based SAPF for PQ improvement in case of medium-voltage distribution sector.

One significant aspect of harmonic current compensation and reference current generation of SAPF unit is the design of the overall control system. The main concern while designing control algorithm is simplicity, robustness and accuracy. At the same point, its effectiveness should be tested under normal supply as well as under distorted source voltage condition.

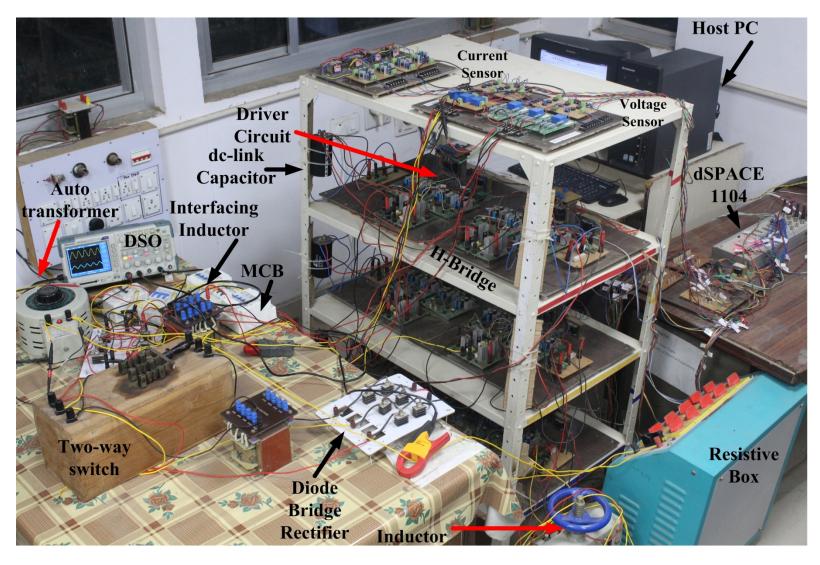

In view of above, the efforts have been made to analyze, design and develop appropriate control algorithm for CHB-MLI based SAPF. Current control plays a significant role for defining current shape and magnitude in case of shunt type active filtering applications. PI compensators are replaced by proportional-resonant (PR) compensator in order to acquire better steady-state performance in AC controllability. Stability of the proposed control theory is checked and analyzed with the help of root-locus analysis. PR compensator based advanced current controller is used in current control loop to introduce infinite gain at selected frequency. This controller facilitates the system operation with superior performance over conventional controller in terms of sinusoidal reference signal tracking capacity and disturbance rejection capability. Detailed simulations are carried out in MATLAB™/ Simulink® and verified experimentally using dSPACE 1104 real-time controller.

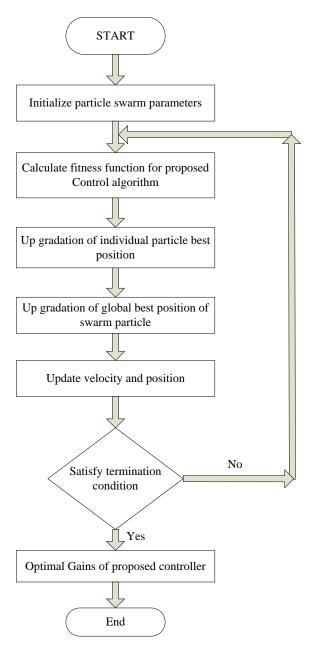

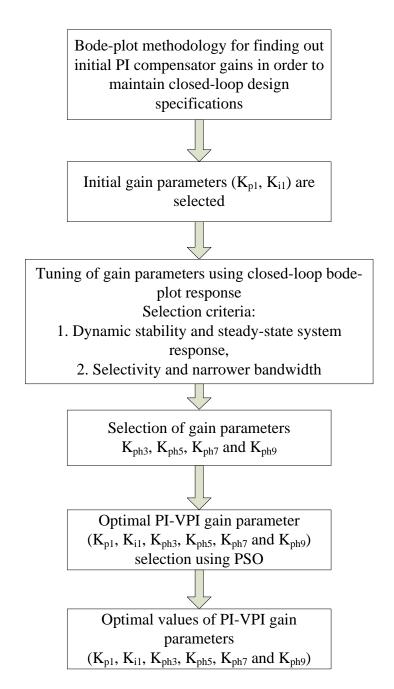

However, use of PR compensator in current control loop causes reduction in stability margin of the closed-loop SAPF system and it is also responsible to create undesired peaks during real-time applications. Therefore, PI-vector-proportional-integral (VPI) compensator based current controller is designed in order to maintain superior SAPF performance during its operation. This compensator is able to mitigate high-frequency components from current control loop and therefore, source current of sinusoidal wave-shape is obtained in case of MLI based SAPF operations. A systematic methodology is presented for tuning PI-VPI compensator parameters using particle swarm optimization (PSO) technique by minimizing source current steady-state error and source current total harmonic distortion. Effectiveness of proposed control has been also thoroughly tested with rigorous simulation and hardware results.

Advanced PLL based control algorithm is used for CHB-MLI based active filtering application which can work under ideal as well as distorted supply voltage conditions. Advanced PLL is capable of exact measurement of phase angle, fundamental component extraction from polluted signal and DC component removal. Eigen value analysis is used as an effective tool to design of constant parameters for this PLL. Detailed simulation and real-time performance analysis of CHB-MLI based SAPF with proposed PLL based control algorithm is tested in different non-linear loading conditions which confirm the effectiveness of the projected control.

CHB-MLI based filtering approach can provide transformer-less interconnection of converters, gives cost-worthy solution and provides better power quality. Therefore, single-phase CHB-MLI based transformer-less grid-tied PV system is proposed so that system can supply active as well as reactive power in day time and can act as SAPF during night time. The proposed grid-tied PV system is rigorously tested with different irradiations in MATLAB<sup>™</sup>/Simulink<sup>®</sup> platform. Transient and steady-state behavior of the proposed system decides effectiveness of the proposed scheme during night-time and in different weather conditions.

To summarize, five-level CHB-MLI based SAPF is designed using MATLAB™/Simulink® and simpower system toolbox. Advanced current controller composed of PR compensator is designed in order to get zero steady-state error in source current. However, use of PR compensator in current control loop is having limitations during real-time applications. Therefore, PI-VPI compensator based current controller is designed in order to maintain zero steady-state error during SAPF performance. An advanced PLL is also designed for CHB-MLI based active filtering application which is able to perform its proper operation in case of normal and distorted source voltage condition. A small-scale prototype of five-level CHB-MLI has been developed in the laboratory, where dSPACE 1104 is used for implementing control algorithms. Finally, use of CHB-MLI based SAPF is extended for grid-tied PV applications for active power injection as well as reactive power minimization. Detailed steady-state and transient performance analysis through simulative and experimental study prove that source current becomes sinusoidal and this is maintained according to IEEE-519 standard under different non-linear loading conditions.

## **CONTENTS**

| ACKNOWLE    | DGEM         | ENTS     |                                             | i      |

|-------------|--------------|----------|---------------------------------------------|--------|

| ABSTRACT    |              |          |                                             | v      |

| CONTENTS    |              |          |                                             | ix     |

| LIST OF FIG | URES         |          |                                             | xv     |

| LIST OF TAB | BLES         |          |                                             | xxix   |

| LIST OF SYM | <b>IBOLE</b> | S        |                                             | XXX    |

| LIST OF ABB | REVI         | ATIONS   |                                             | xxxiii |

| CHAPTER 1   | INTR         | ODUCT    | TION                                        | 1      |

|             | 1.1          | Overvi   | ew                                          | 1      |

|             | 1.2          | Power    | Quality Issues                              | 4      |

|             |              | 1.2.1    | Causes of Harmonics                         | 5      |

|             |              | 1.2.2    | Effects of Harmonics                        | 6      |

|             | 1.3          | Power    | Quality Standards and Indices               | 7      |

|             | 1.4          | Curren   | t Harmonic Compensation Techniques          | 8      |

|             |              | 1.4.1    | Passive Filters                             | 8      |

|             |              | 1.4.2    | Active Filtering Approach                   | 10     |

|             | 1.5          | Limitat  | ions of Conventional APF in Medium to High  | 11     |

|             |              | Voltage  | e Systems                                   |        |

|             | 1.6          | MLI B    | ased SAPF for High Voltage System           | 12     |

|             | 1.7          | Organi   | zation of Thesis                            | 13     |

| CHAPTER 2   | LITE         | RATUR    | E REVIEW                                    | 17     |

|             | 2.1          | Introdu  | ction                                       | 17     |

|             | 2.2          | Literati | are Review                                  | 18     |

|             |              | 2.2.1    | Multilevel Inverter (MLI)                   | 21     |

|             |              |          | 2.2.1.1 Conventional MLI Topologies         | 22     |

|             |              |          | 2.2.1.2 Hybrid MLI Topologies               | 26     |

|             |              | 2.2.2    | Review based on Topologies of MLI Based APF | 26     |

|             |              | 2.2.3    | Control Strategies of MLI based APF         | 39     |

|           |      | 2.2.4  | Applica     | ation and Pract  | ical Implementation of   | MLI 59       |

|-----------|------|--------|-------------|------------------|--------------------------|--------------|

|           |      |        | based A     | APF              |                          |              |

|           | 2.3  | Scope  | of the W    | ork and Author   | 's Contribution          | 62           |

|           | 2.4  | Concl  | usion       |                  |                          | 66           |

| CHAPTER 3 | LABO | ORATO  | ORY P       | PROTOTYPE        | DEVELOPMENT              | <b>OF</b> 69 |

|           | CASO | CADED  | H-BRID      | GE (CHB)- M      | LI BASED SAPF            |              |

|           | 3.1  | Introd | uction      |                  |                          | 69           |

|           | 3.2  | Devel  | opment of   | f System Hardw   | vare                     | 72           |

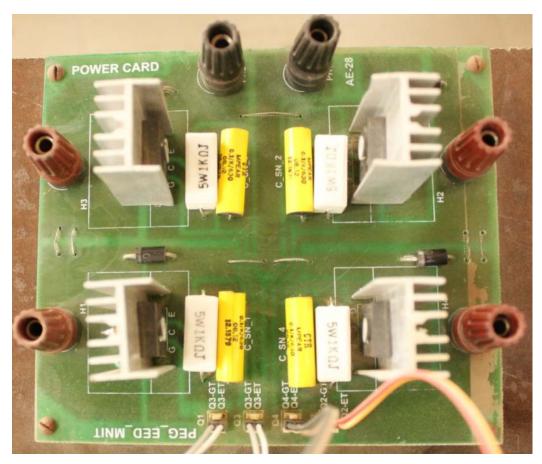

|           |      | 3.2.1  | Fabricat    | ion of Five-leve | el CHB Inverter          | 72           |

|           |      |        | 3.2.1.1     | Selection of S   | emiconductor Switch      | 73           |

|           |      |        | 3.2.1.2     | Snubber Circu    | nit Design               | 73           |

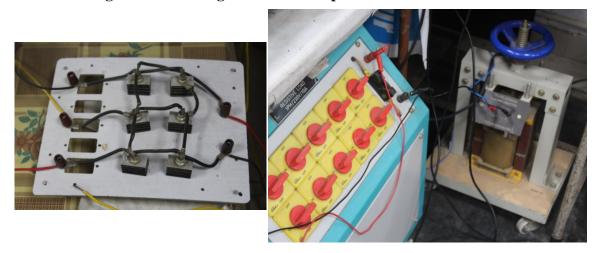

|           |      | 3.2.2  | Design      | of Non-linear L  | oading                   | 75           |

|           |      | 3.2.3  | Measure     | ement of Inte    | erface Circuit for Sy    | stem 76      |

|           |      |        | Perform     | ance             |                          |              |

|           |      |        | 3.2.3.1     | Current Sens     | or Circuit               | 76           |

|           |      |        | 3.2.3.2     | Voltage Sens     | or Circuit               | 77           |

|           |      |        | 3.2.3.3     | Sensor Ampl      | ification Circuit        | 78           |

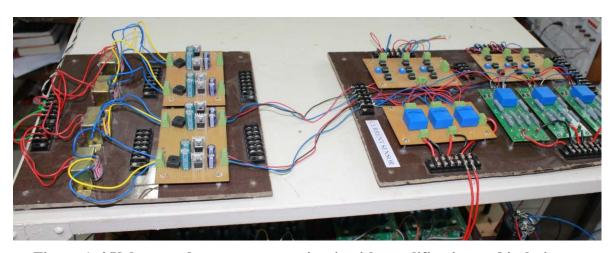

|           |      | 3.2.4  | Control     | Scheme Deploy    | yment using dSPACE 1     | 104 81       |

|           |      | 3.2.5  | Design      | of Gate Driver ( | Circuit for CHB-MLI      | 82           |

|           |      |        | 3.2.5.1     | Pulse Amplif     | ication and Isolation Ci | rcuit 82     |

|           |      |        | 3.2.5.2     | Dead Band C      | Circuit                  | 84           |

|           | 3.3  | Concl  | usion       |                  |                          | 87           |

| CHAPTER 4 | PRO  | PORTI  | ONAL-R      | ESONANT          | (PR) COMPENSA            | ATOR 89      |

|           | BASI | ED ADV | ANCED       | CURRENT C        | CONTROL STRATEG          | Y            |

|           | 4.1  | Introd | uction      |                  |                          | 89           |

|           | 4.2  | System | n Configu   | ıration          |                          | 93           |

|           | 4.3  | Model  | ling of Pro | oportional-Reso  | onant (PR) Compensato    | r 94         |

|           |      | 4.3.1  | Introduc    | ction            |                          | 94           |

|           |      | 4.3.2  | Modelin     | ng and Stal      | bility Analysis of       | PR 95        |

|           |      |        | Comper      | ısator           |                          |              |

|           | 4.4                         | Design and Stability Analysis of Proposed Closed-loop                                                                                                                                                                                                                                                                                                                                                             | 100                                                         |

|-----------|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

|           |                             | Control System                                                                                                                                                                                                                                                                                                                                                                                                    |                                                             |

|           |                             | 4.4.1 Advanced SRF theory composed of PR                                                                                                                                                                                                                                                                                                                                                                          | 100                                                         |

|           |                             | Compensator                                                                                                                                                                                                                                                                                                                                                                                                       |                                                             |

|           |                             | 4.4.2 Stability Analysis of Proposed Control Algorithm                                                                                                                                                                                                                                                                                                                                                            | 102                                                         |

|           |                             | 4.4.3 Design of Current Controller Constants                                                                                                                                                                                                                                                                                                                                                                      | 110                                                         |

|           | 4.5                         | Performance Evaluation of Proposed Control using                                                                                                                                                                                                                                                                                                                                                                  | 114                                                         |

|           |                             | MATLAB                                                                                                                                                                                                                                                                                                                                                                                                            |                                                             |

|           |                             | 4.5.1 Uncontrolled Rectifier and R-L Loading                                                                                                                                                                                                                                                                                                                                                                      | 114                                                         |

|           |                             | 4.5.2 Uncontrolled Rectifier and R-C Loading                                                                                                                                                                                                                                                                                                                                                                      | 119                                                         |

|           | 4.6                         | Hardware Implementation of Proposed Control using                                                                                                                                                                                                                                                                                                                                                                 | 123                                                         |

|           |                             | dSPACE 1104                                                                                                                                                                                                                                                                                                                                                                                                       |                                                             |

|           |                             | 4.6.1 Uncontrolled Rectifier and R-L Loading                                                                                                                                                                                                                                                                                                                                                                      | 125                                                         |

|           |                             | 4.6.2 Uncontrolled Rectifier and R-C Loading                                                                                                                                                                                                                                                                                                                                                                      | 127                                                         |

|           | 4.7                         | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                        | 130                                                         |

|           |                             |                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                             |

| CHAPTER 5 | PSO A                       | ASSISTED PI-VPI COMPENSATOR BASED CONTROL                                                                                                                                                                                                                                                                                                                                                                         | 131                                                         |

| CHAPTER 5 |                             | ASSISTED PI-VPI COMPENSATOR BASED CONTROL ATEGY                                                                                                                                                                                                                                                                                                                                                                   | 131                                                         |

| CHAPTER 5 |                             |                                                                                                                                                                                                                                                                                                                                                                                                                   | 131<br>131                                                  |

| CHAPTER 5 | STRA                        | ATEGY                                                                                                                                                                                                                                                                                                                                                                                                             |                                                             |

| CHAPTER 5 | <b>STR</b> A 5.1            | ATEGY Introduction                                                                                                                                                                                                                                                                                                                                                                                                | 131                                                         |

| CHAPTER 5 | <b>STR</b> <i>A</i> 5.1 5.2 | ATEGY Introduction Proposed Five-level CHB-MLI based SAPF System                                                                                                                                                                                                                                                                                                                                                  | 131<br>133                                                  |

| CHAPTER 5 | <b>STR</b> <i>A</i> 5.1 5.2 | ATEGY Introduction Proposed Five-level CHB-MLI based SAPF System Working Principle of Proportional Integral Vector                                                                                                                                                                                                                                                                                                | 131<br>133                                                  |

| CHAPTER 5 | 5.1<br>5.2<br>5.3           | Introduction Proposed Five-level CHB-MLI based SAPF System Working Principle of Proportional Integral Vector Proportional Integral Compensator                                                                                                                                                                                                                                                                    | 131<br>133<br>136                                           |

| CHAPTER 5 | 5.1<br>5.2<br>5.3           | Introduction Proposed Five-level CHB-MLI based SAPF System Working Principle of Proportional Integral Vector Proportional Integral Compensator Improved Closed-loop Control Scheme for Active Filtering                                                                                                                                                                                                           | 131<br>133<br>136                                           |

| CHAPTER 5 | 5.1<br>5.2<br>5.3           | Introduction Proposed Five-level CHB-MLI based SAPF System Working Principle of Proportional Integral Vector Proportional Integral Compensator Improved Closed-loop Control Scheme for Active Filtering 5.4.1 Current Reference Generation Technique                                                                                                                                                              | 131<br>133<br>136<br>140                                    |

| CHAPTER 5 | 5.1<br>5.2<br>5.3           | Introduction Proposed Five-level CHB-MLI based SAPF System Working Principle of Proportional Integral Vector Proportional Integral Compensator Improved Closed-loop Control Scheme for Active Filtering 5.4.1 Current Reference Generation Technique 5.4.2 Closed-loop Performance of PI-VPI Compensator                                                                                                          | 131<br>133<br>136<br>140                                    |

| CHAPTER 5 | 5.1<br>5.2<br>5.3           | Introduction Proposed Five-level CHB-MLI based SAPF System Working Principle of Proportional Integral Vector Proportional Integral Compensator Improved Closed-loop Control Scheme for Active Filtering 5.4.1 Current Reference Generation Technique 5.4.2 Closed-loop Performance of PI-VPI Compensator based Current Controller                                                                                 | 131<br>133<br>136<br>140<br>140<br>142                      |

| CHAPTER 5 | 5.1<br>5.2<br>5.3<br>5.4    | Introduction Proposed Five-level CHB-MLI based SAPF System Working Principle of Proportional Integral Vector Proportional Integral Compensator Improved Closed-loop Control Scheme for Active Filtering 5.4.1 Current Reference Generation Technique 5.4.2 Closed-loop Performance of PI-VPI Compensator based Current Controller 5.4.3 DFRM-3 φ-pPLL Structure                                                   | 131<br>133<br>136<br>140<br>140<br>142<br>148<br>151<br>152 |

| CHAPTER 5 | 5.1<br>5.2<br>5.3<br>5.4    | Introduction Proposed Five-level CHB-MLI based SAPF System Working Principle of Proportional Integral Vector Proportional Integral Compensator Improved Closed-loop Control Scheme for Active Filtering 5.4.1 Current Reference Generation Technique 5.4.2 Closed-loop Performance of PI-VPI Compensator based Current Controller 5.4.3 DFRM-3 φ -pPLL Structure Gain Parameter Calculation of PI-VPI Compensator | 131<br>133<br>136<br>140<br>140<br>142<br>148<br>151        |

|           | 5.6  | Performa  | ance Assessment of Proposed Control using     | 158 |

|-----------|------|-----------|-----------------------------------------------|-----|

|           |      | MATLA     | AB/ Simulink                                  |     |

|           |      | 5.6.1     | Uncontrolled Rectifier and R-L Loading        | 158 |

|           |      | 5.6.2     | Uncontrolled Rectifier and R-C Loading        | 162 |

|           | 5.7  | Experim   | nental Validation of Proposed Control using   | 166 |

|           |      | dSPACE    | E 1104                                        |     |

|           |      | 5.7.1     | Uncontrolled Rectifier and R-L Loading        | 167 |

|           |      | 5.7.2     | Uncontrolled Rectifier and R-C Loading        | 169 |

|           | 5.8  | Conclusi  | ion                                           | 173 |

| CHAPTER 6 | DESI | GN OF     | ADVANCED PLL BASED IMPROVED                   | 175 |

|           | SYNO | CHRONO    | OUS REFERENCE FRAME CONTROL                   |     |

|           | ALG  | ORITHM    | [                                             |     |

|           | 6.1  | Introduct | tion                                          | 175 |

|           | 6.2  | Design a  | and Development of Projected PLL              | 178 |

|           |      | 6.2.1     | Mathematical Modeling using Transfer Function | 180 |

|           |      |           | Approach                                      |     |

|           |      | 6.2.2     | Selection of Gain Parameters in Advanced PLL  | 181 |

|           |      | 6.2.3     | Stability Analysis using Transfer Function    | 184 |

|           |      |           | Approach                                      |     |

|           | 6.3  | Design    | and Development of Advanced Synchronous       | 188 |

|           |      | Reference | ce Frame Control Algorithm                    |     |

|           |      | 6.3.1     | Reference Current Generation                  | 188 |

|           |      | 6.3.2     | DC-link Voltage Control                       | 190 |

|           |      | 6.3.3     | Gate Pulse Generation                         | 191 |

|           |      |           |                                               | 192 |

|           | 6.4  | •         | · ·                                           | 194 |

|           |      |           | MATLAB/ Simulink                              |     |

|           |      |           |                                               | 198 |

|           |      |           | Distorted Supply Voltage                      |     |

|           |      | 6.4.2     | Uncontrolled Converter with R-C Load and      | 206 |

## Distorted Supply Voltage

|             | 6.5  | Labor   | ratory Prototype Development of Modified SRF   | 214 |

|-------------|------|---------|------------------------------------------------|-----|

|             |      | Theo    | y with Advanced PLL                            |     |

|             |      | 6.5.1   | Uncontrolled Converter with R-L Load           | 219 |

|             |      | 6.5.2   | Uncontrolled Converter with R-C Load           | 224 |

|             | 6.6. | Conc    | usion                                          | 227 |

| CHAPTER 7   | ACT  | IVE A   | ND REACTIVE POWER MANAGEMENT OF                | 229 |

|             | CHB  | 8-MLI B | SASED GRID-TIED PHOTOVOLTAIC                   |     |

|             | 7.1  | Introdu | action                                         | 229 |

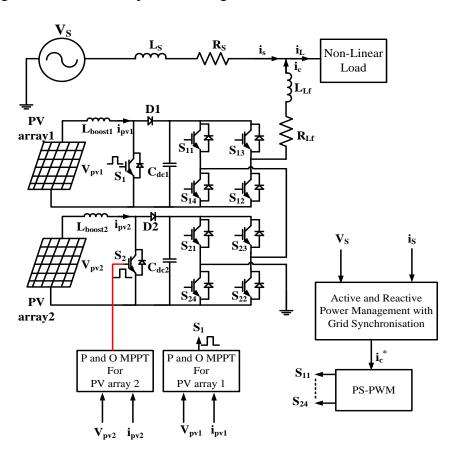

|             | 7.2  | Systen  | n Description                                  | 231 |

|             | 7.3  | Model   | ing of Proposed System                         | 232 |

|             |      | 7.3.1   | Modeling of PV Array                           | 232 |

|             |      | 7.3.2   | Modeling of DC-DC Boost Converter              | 232 |

|             |      | 7.3.3   | DC Bus Voltage Selection                       | 232 |

|             |      | 7.3.4   | DC-link capacitor selection                    | 233 |

|             |      | 7.3.5   | Inductor Selection                             | 233 |

|             | 7.4  | Contro  | l Strategy                                     | 233 |

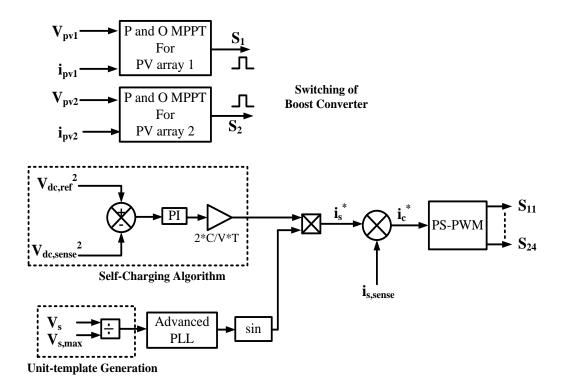

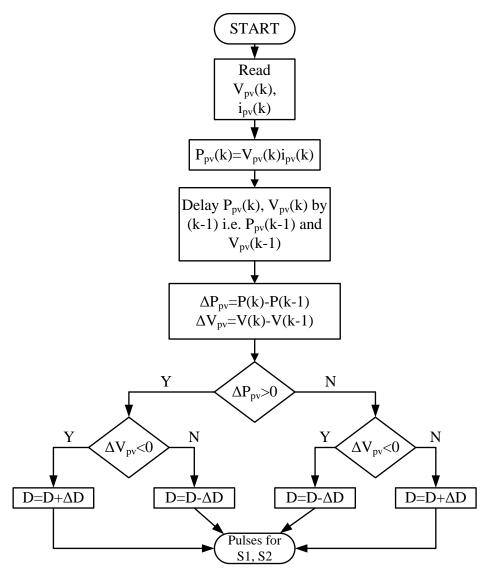

|             |      | 7.4.1   | P and O MPPT Control                           | 234 |

|             |      | 7.4.2   | DC-link Voltage Control                        | 236 |

|             |      | 7.4.3   | Phase Angle Control using Advanced PLL         | 238 |

|             |      | 7.4.4   | Gate Pulse Generation using PS-PWM             | 238 |

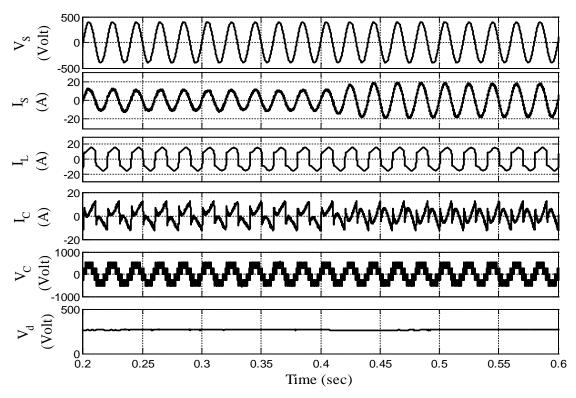

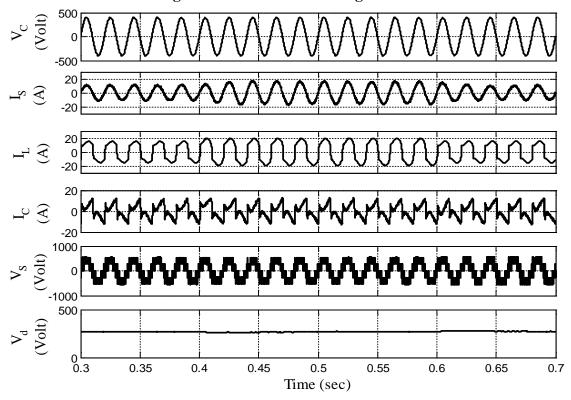

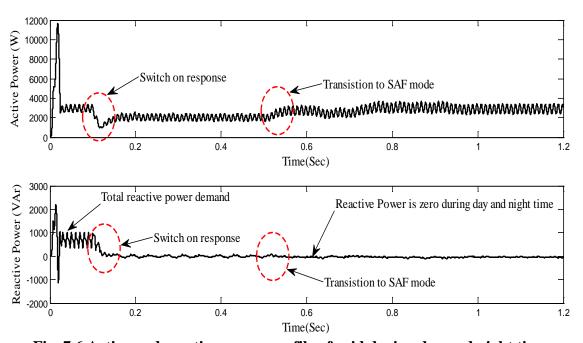

|             | 7.5  | Perfor  | mance Assessment of CHB-MLI based Grid-tied PV | 239 |

|             |      | Systen  | n using MATLAB/ Simulink                       |     |

|             | 7.6  | Conclu  | asion                                          | 248 |

| CHAPTER 8   | CON  | ICLUSI  | ON AND FUTURE SCOPE                            | 251 |

|             | 8.1  | Conclu  | asion                                          | 251 |

|             | 8.2  | Future  | Scope                                          | 255 |

| LIST OF PUB | LICA | TIONS   | FROM RESEARCH WORK                             | 259 |

| BIBLIOGRAP  | НY   |         |                                                | 261 |

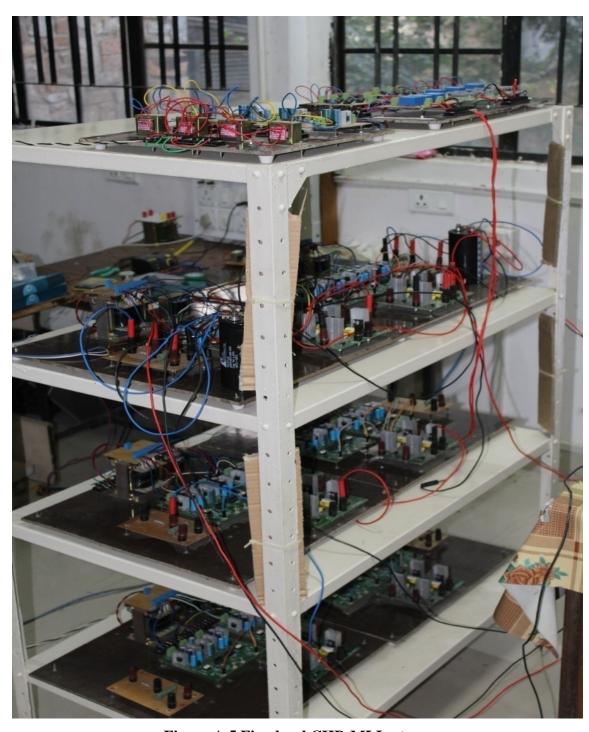

| APPENDIX A | Hardware Circuit and Set-Up Photograph | 285 |

|------------|----------------------------------------|-----|

| APPENDIX B | Design of Power Circuit Parameters     | 291 |

| APPENDIX C | Parameters used for Simulation Study   | 292 |

| APPENDIX D | Parameters used for Experimental Study | 293 |

## LIST OF FIGURES

| Figure No. | Title                                                                                                                                                                                       | Page No. |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

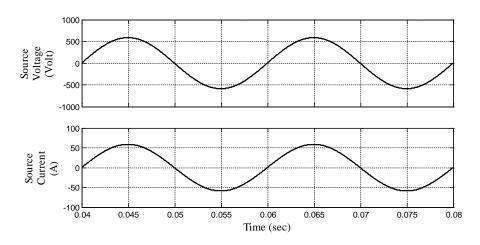

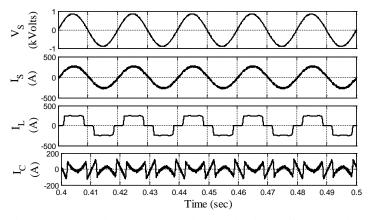

| Figure 1.1 | Source voltage and source current waveforms due to linear loads                                                                                                                             | 2        |

| Figure 1.2 | Source voltage and source current waveforms due to non-linear loads                                                                                                                         | 2        |

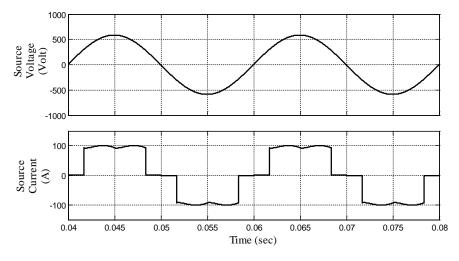

| Figure 1.3 | Sources of harmonics in power system                                                                                                                                                        | 5        |

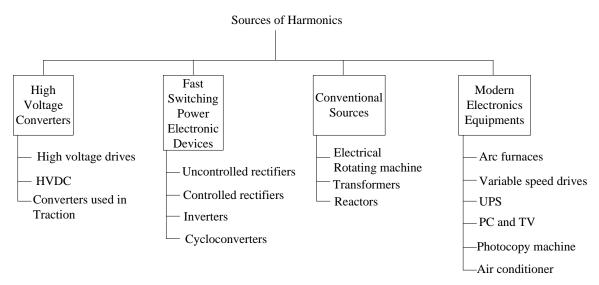

| Figure 1.4 | (a) Single-tuned filter, (b) double-tuned filter, and (c) second-order high pass filter                                                                                                     | 9        |

| Figure 1.5 | Basic compensation principle of shunt APF                                                                                                                                                   | 10       |

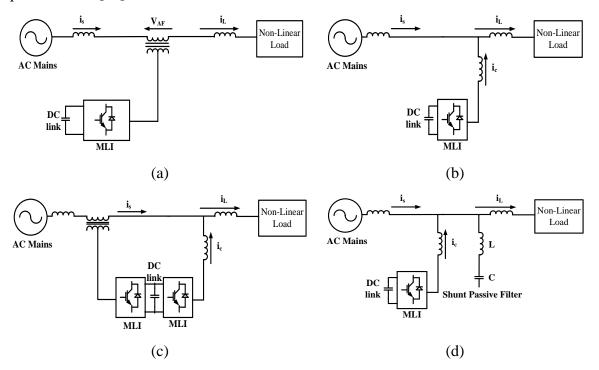

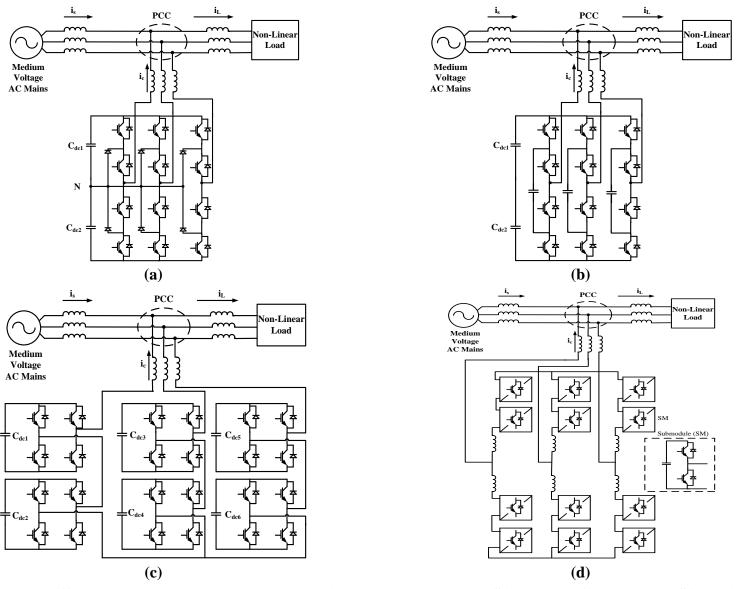

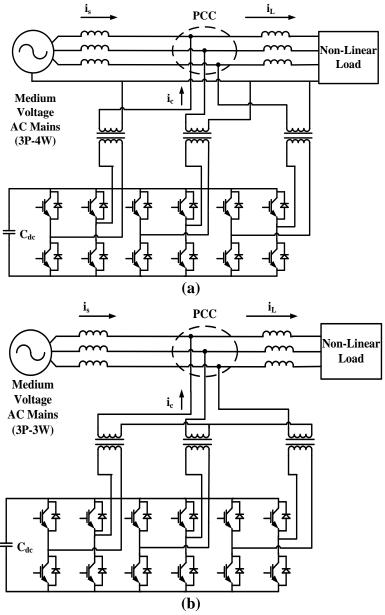

| Figure 2.1 | <ul><li>(a) Block diagram representation of MLI based series APF,</li><li>(b) MLI based shunt APF, (c) MLI based UPQC, and (d) MLI based hybrid APF</li></ul>                               | 20       |

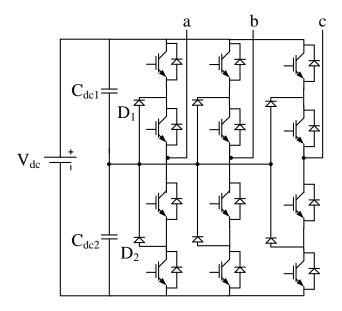

| Figure 2.2 | Diode-clamped multilevel inverter                                                                                                                                                           | 22       |

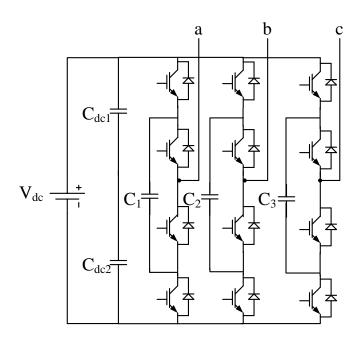

| Figure 2.3 | Flying-capacitor multilevel inverter                                                                                                                                                        | 23       |

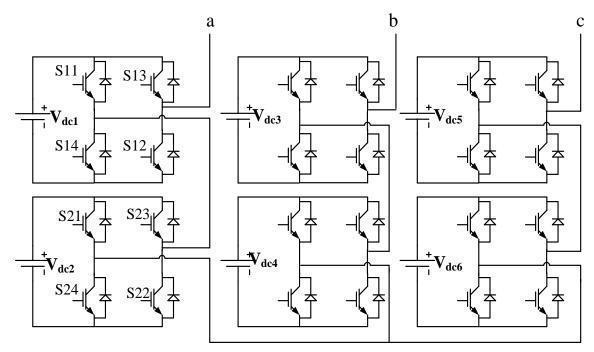

| Figure 2.4 | Cascaded H-bridge multilevel inverter                                                                                                                                                       | 25       |

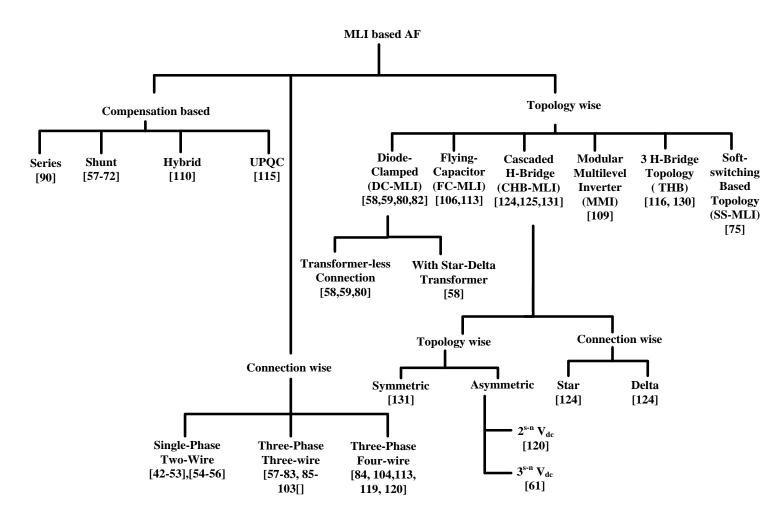

| Figure 2.5 | Topological classification of MLI based SAPF                                                                                                                                                | 30       |

| Figure 2.6 | Different three-phase, three-wire topologies used as MLI based SAPF (a) DC-MLI based SAPF, (b) FC-MLI based SAPF, (c) symmetrical star-connected CHB-MLI based SAPF, and (d) MMI based SAPF | 33       |

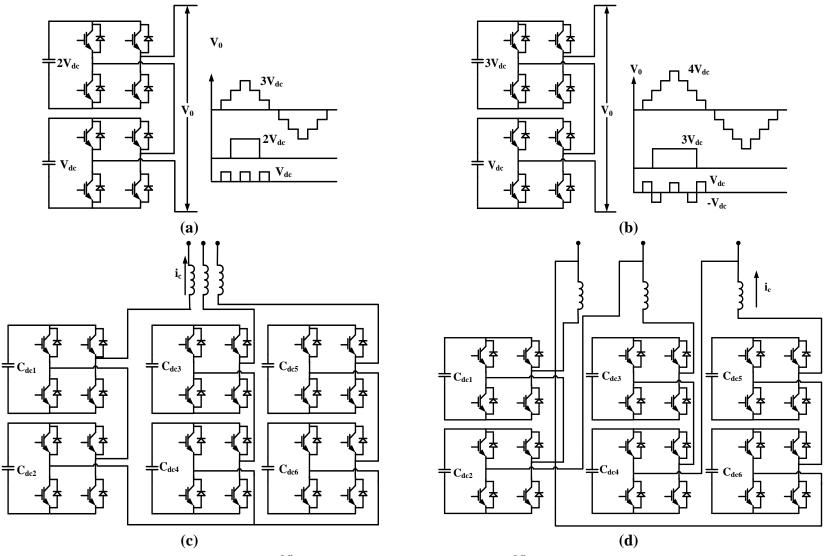

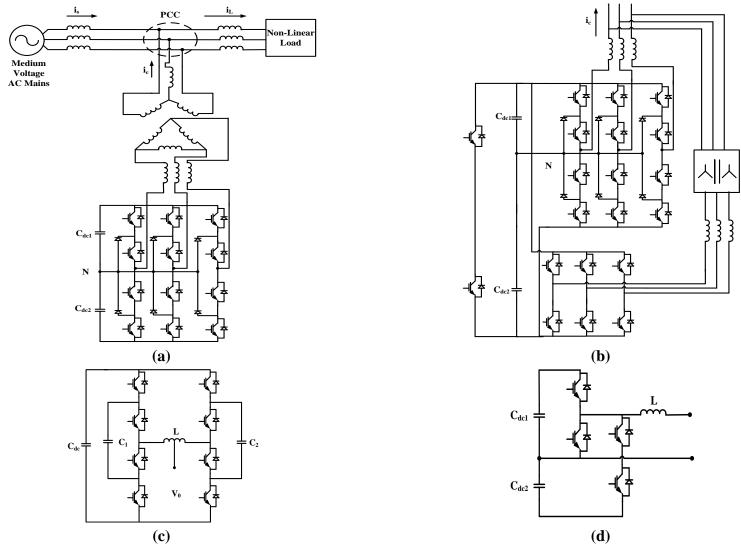

| Figure 2.7 | (a) Asymmetric CHB-MLI (2 <sup>s-n</sup> ), (b) asymmetric CHB-MLI (3 <sup>s-n</sup> ), (c) star connection of CHB-MLI, and (d) delta connection of CHB-MLI                                 | 34       |

| Figure 2.8 | Three-phase H-bridge topology for (a) three-phase, three-wire                                                                                                                               | 35       |

|             | system, and (b) three-phase, four-wire system                                                                                                                                                                                                                   |    |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2.9  | <ul><li>(a) Diode-clamped inverter with line-frequency transformer,</li><li>(b) parallel connection of DC-MLI with two-level inverter, (c)</li><li>reduced switch topology MLI for shunt APF application, and</li><li>(d) zero-voltage transition MLI</li></ul> | 36 |

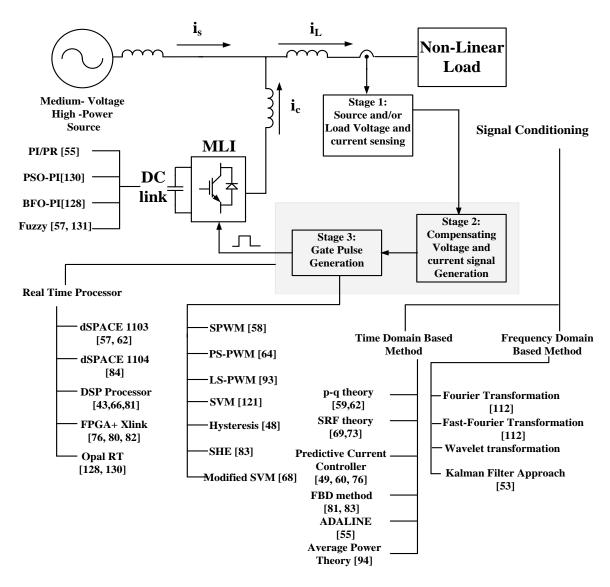

| Figure 2.10 | Block diagram of detailed control system of MLI based shunt APF with different techniques in literature                                                                                                                                                         | 41 |

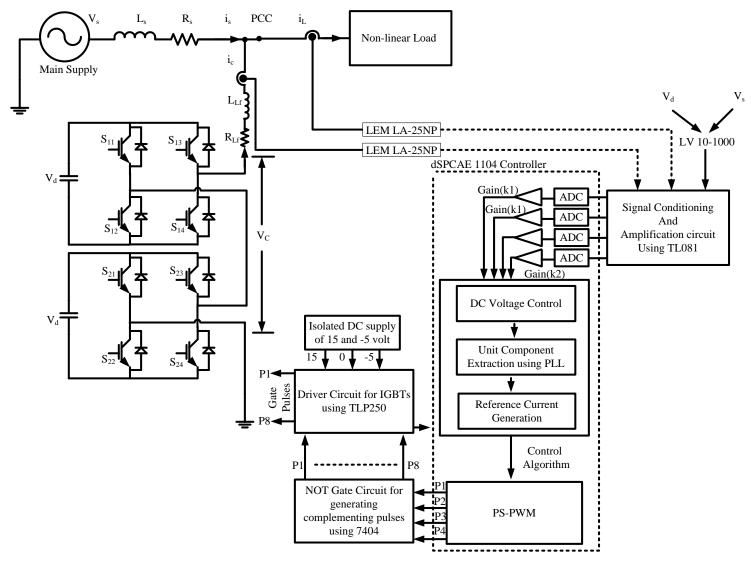

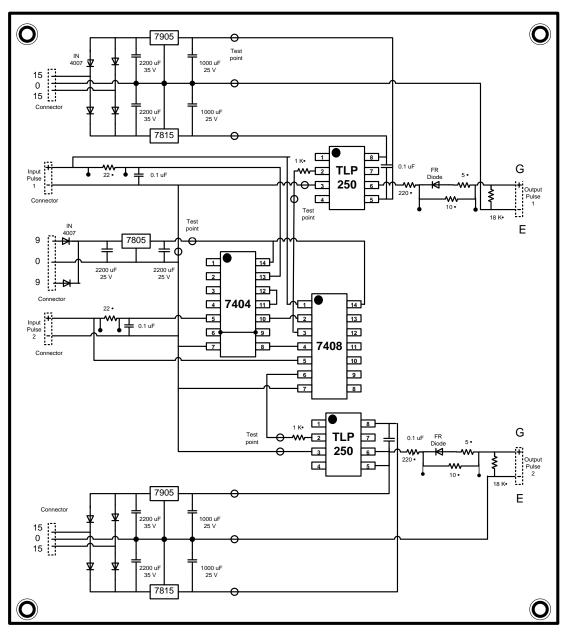

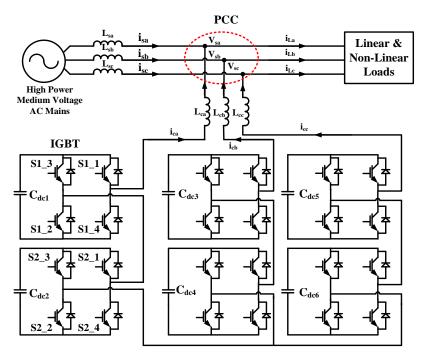

| Figure 3.1  | Hardware schematic diagram of single-phase five-level CHB-MLI based shunt active power filter                                                                                                                                                                   | 71 |

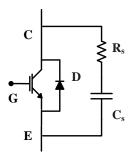

| Figure 3.2  | Snubber circuit with IGBT                                                                                                                                                                                                                                       | 74 |

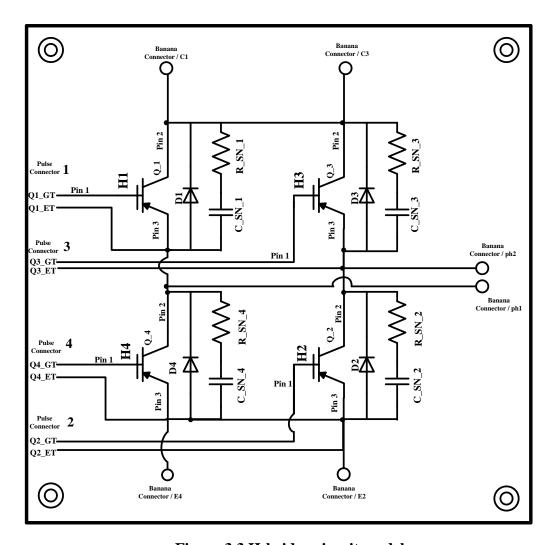

| Figure 3.3  | H-bridge circuit model                                                                                                                                                                                                                                          | 75 |

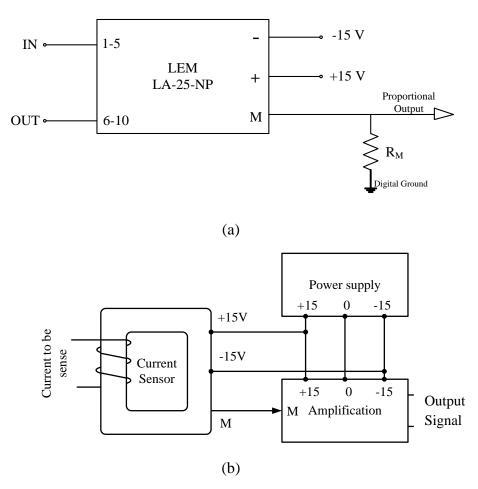

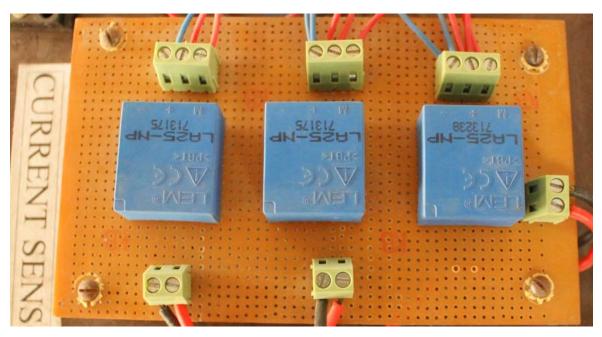

| Figure 3.4  | (a) Schematic diagram of current sensor LA-25 NP, and (b) circuit configuration of current sensor circuit with amplification                                                                                                                                    | 77 |

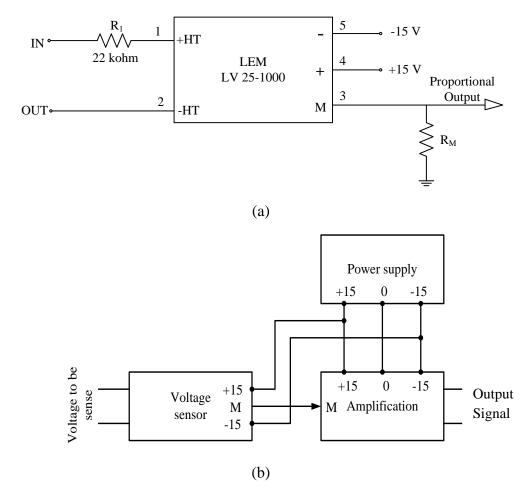

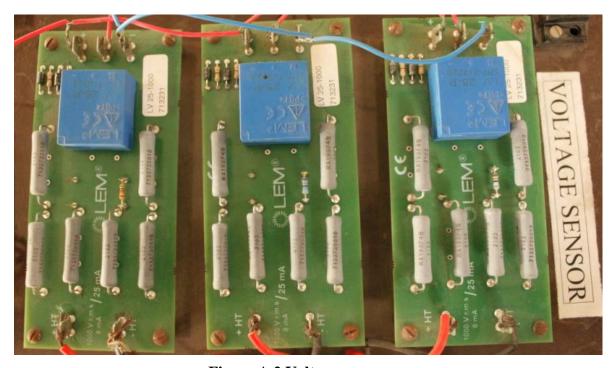

| Figure 3.5  | (a) Schematic diagram of voltage sensor LV 25-1000, and (b) circuit configuration of voltage sensor circuit with amplification                                                                                                                                  | 79 |

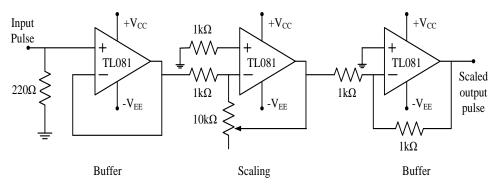

| Figure 3.6  | Signal amplification circuit                                                                                                                                                                                                                                    | 80 |

| Figure 3.7  | Sensor amplification circuit output of (a) current amplification circuit, and (b) voltage amplification circuit                                                                                                                                                 | 80 |

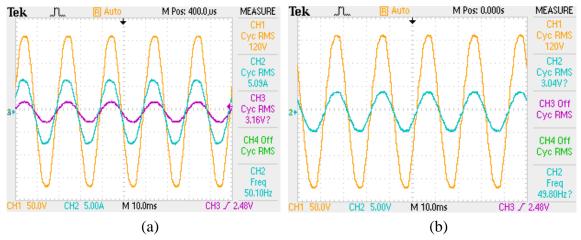

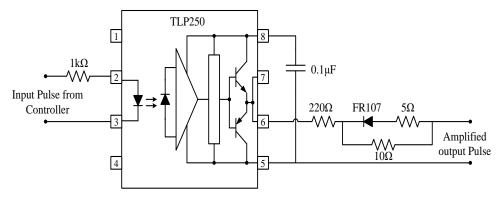

| Figure 3.8  | Total development environment of dSPACE 1104 with MATLAB                                                                                                                                                                                                        | 82 |

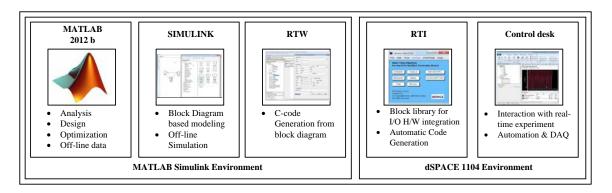

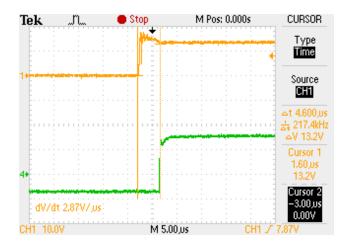

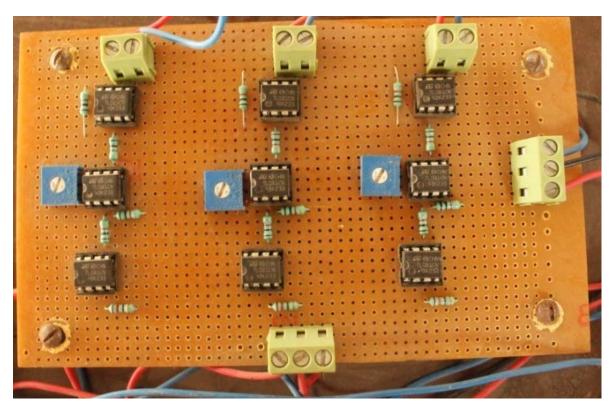

| Figure 3.9  | TLP 250 based gate pulse amplification and isolation circuit                                                                                                                                                                                                    | 83 |

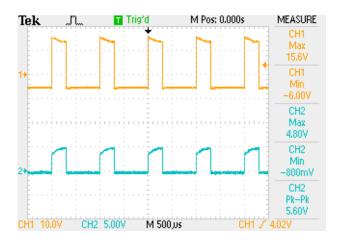

| Figure 3.10 | Hardware results of gate driver amplification and isolation circuit                                                                                                                                                                                             | 84 |

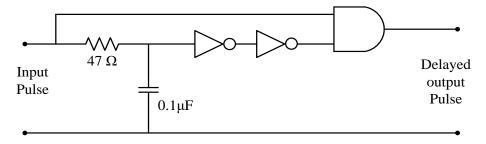

| Figure 3.11 | Circuit diagram of dead-band circuitry                                                                                                                                                                                                                          | 85 |

| Figure 3.12 | Hardware result of dead band circuit                                                                                                                                                                                              | 85  |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

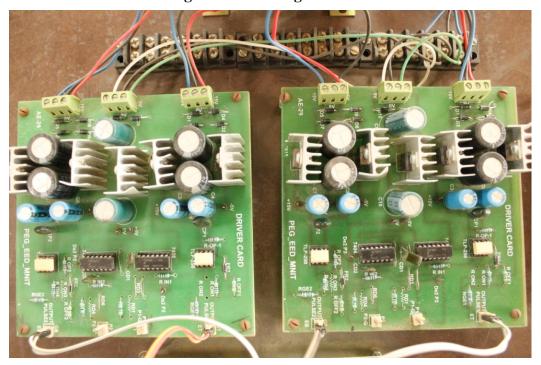

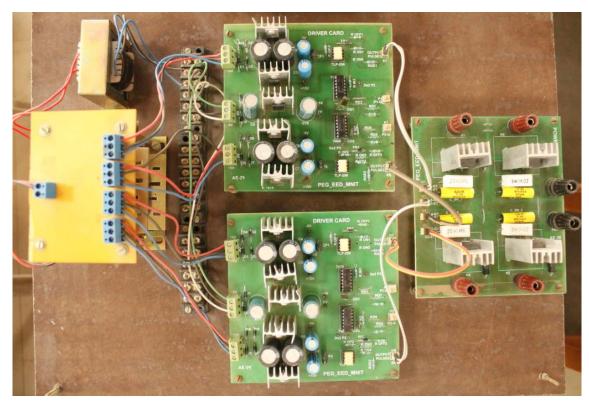

| Figure 3.13 | Driver circuit developed in the laboratory for two IGBTs of one leg of inverter circuit                                                                                                                                           | 86  |

| Figure 4.1  | Five-level CHB-MLI based SAPF                                                                                                                                                                                                     | 94  |

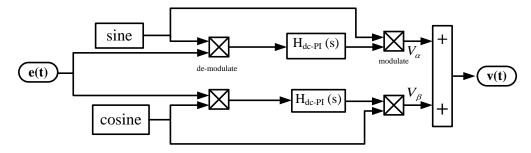

| Figure 4.2  | Modulation and demodulation of PR compensator                                                                                                                                                                                     | 95  |

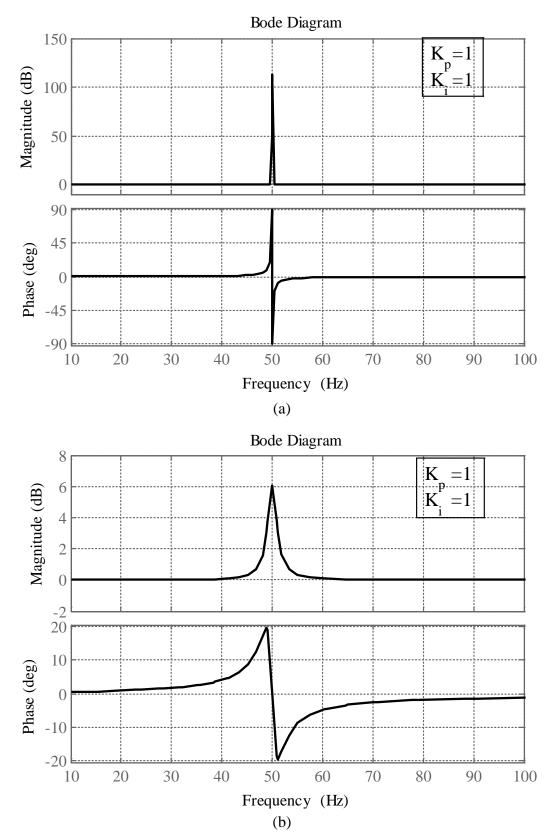

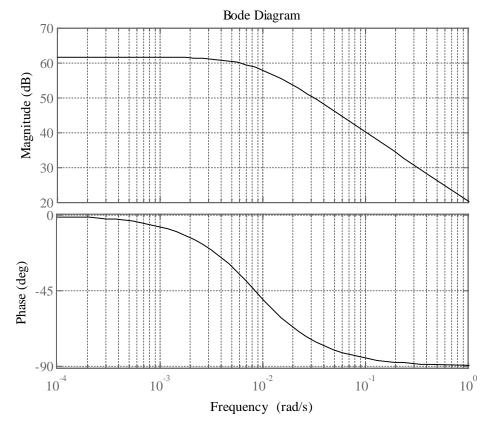

| Figure 4.3  | Bode-plot of proportional-resonant compensator (a) in ideal condition, and (b) in practical condition                                                                                                                             | 99  |

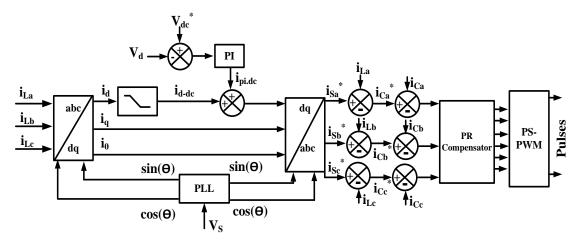

| Figure 4.4  | SRF based advanced control theory for CHB-MLI based SAPF                                                                                                                                                                          | 101 |

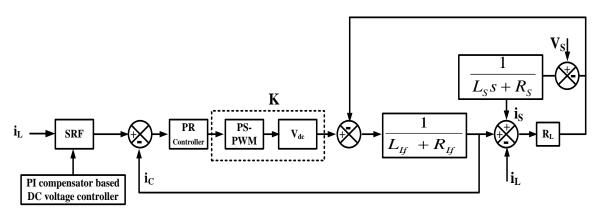

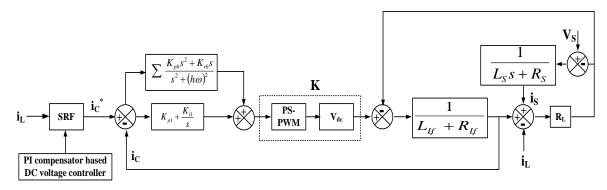

| Figure 4.5  | Closed loop control algorithm applied to CHB-MLI based SAPF                                                                                                                                                                       | 102 |

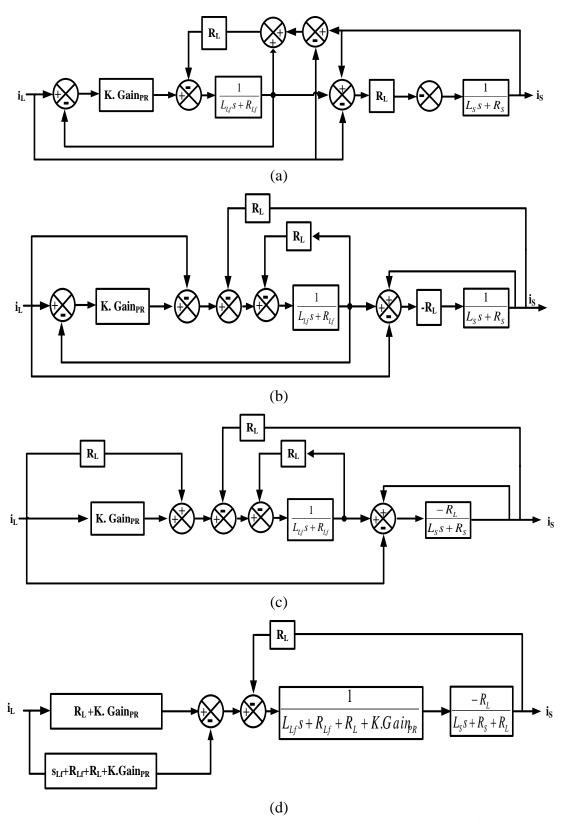

| Figure 4.6  | (a) Equivalent loop diagram considering inverter and PS-PWM gain parameter, (b) rearranged loop diagram, (c) simplified loop diagram by rearranging adder blocks, and (d) simplified closed loop diagram by solving feedback loop | 103 |

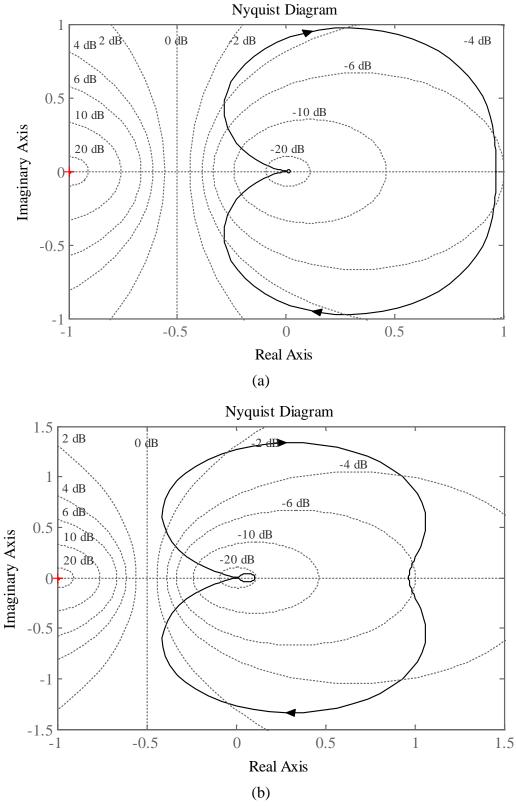

| Figure 4.7  | Nyquist diagram of (a) ideal PR compensator based advanced current controller, and (b) practical purpose PR compensator based advanced current controller                                                                         | 108 |

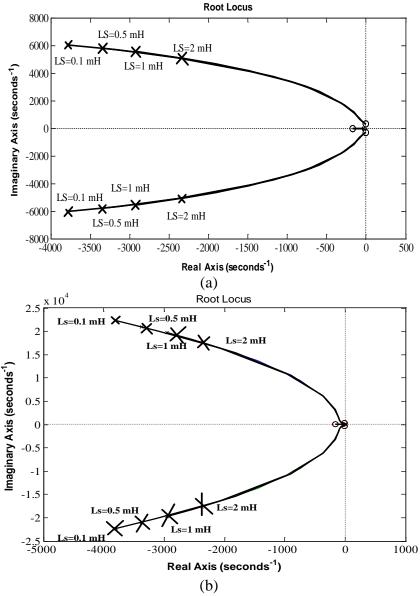

| Figure 4.8  | Root-locus diagram with variation of grid-impedance in case of (a) ideal PR compensator based control, and (b) practical purpose PR compensator based control                                                                     | 109 |

| Figure 4.9  | Bode plot of $G_1(s)$                                                                                                                                                                                                             | 111 |

| Figure 4.10 | Bode-plot diagram of advanced current controller transfer<br>function (a) ideal PR compensator based current control loop,<br>and (b) non-ideal PR compensator based current control loop                                         | 113 |

| Figure 4.11 | Steady-state simulation results of CHB-MLI based SAPF with                                                                                                                                                                        | 115 |

|             | PR compensator based advanced current controller under R-L loading condition                                                                                                                                                             |     |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

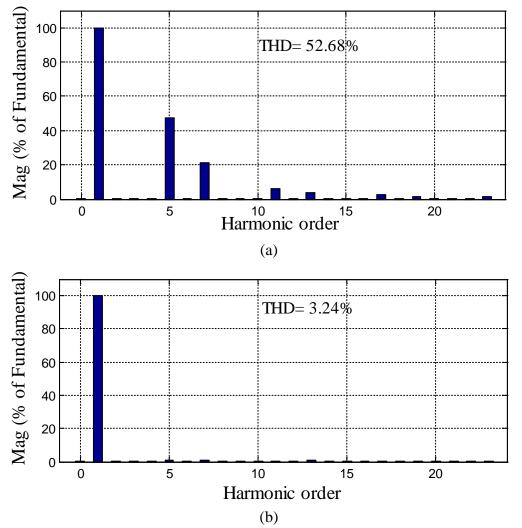

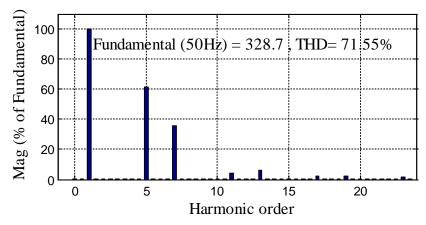

| Figure 4.12 | THD profile of source current with R-L load (a) before compensation, and (b) after compensation                                                                                                                                          | 116 |

| Figure 4.13 | Transient performance of MLI based SAPF during load increment with R-L loading condition                                                                                                                                                 | 117 |

| Figure 4.14 | Transient performance of MLI based SAPF during load decrement with R-L loading condition                                                                                                                                                 | 117 |

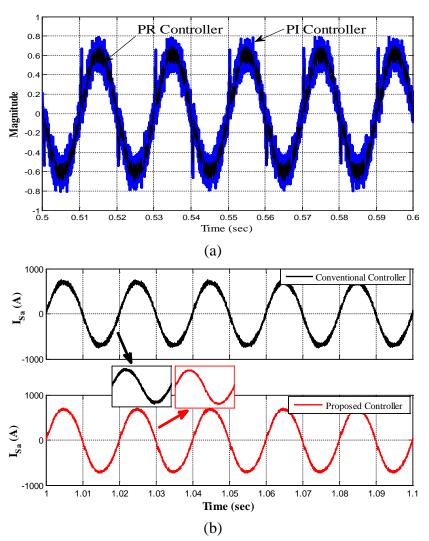

| Figure 4.15 | Performance comparison of proposed controller with conventional current controller for MLI based SAPF system (a) error signal magnitude comparison, and (b) source current wave shape comparison                                         | 118 |

| Figure 4.16 | Steady-state simulation results of CHB-MLI based SAPF with advanced current controller under R-C loading condition                                                                                                                       | 119 |

| Figure 4.17 | THD profile of source current with R-C loading (a) before compensation, and (b) after compensation                                                                                                                                       | 120 |

| Figure 4.18 | Transient performance of MLI based SAPF during load increment with R-C loading condition                                                                                                                                                 | 122 |

| Figure 4.19 | Transient performance of MLI based SAPF during load decrement with R-C loading condition                                                                                                                                                 | 122 |

| Figure 4.20 | Proposed control theory for five-level single-phase CHB-MLI                                                                                                                                                                              | 124 |

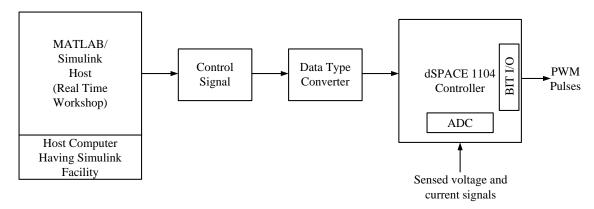

| Figure 4.21 | Block diagram of co-simulation between dSPACE 1104 and MATLAB                                                                                                                                                                            | 125 |

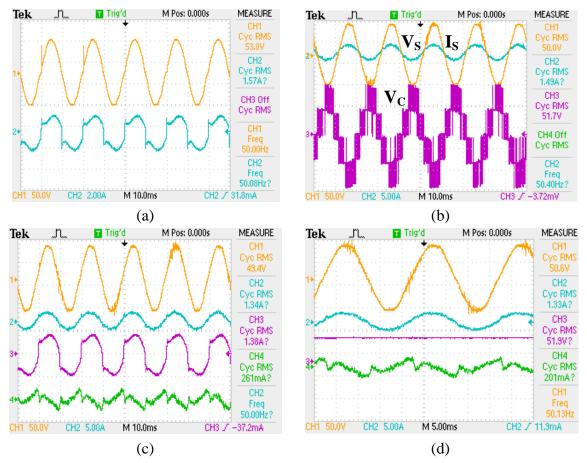

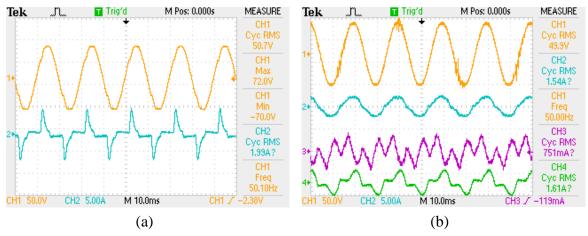

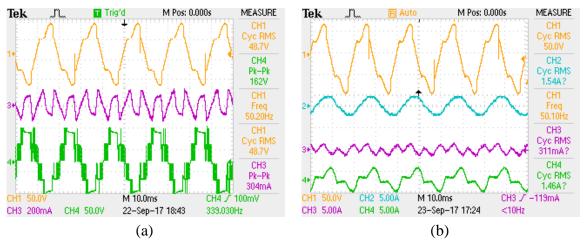

| Figure 4.22 | Experimental waveforms of CHB-MLI based SAPF with proposed controller under R-L loading (a) VS and non-linear source current (IS) (CH1: 50 V/ div., CH2: 5 A/ div.), (b) MLI voltage waveform with source voltage (CH1: 50 V/ div., CH2: | 126 |

|             | 5 A/ div., CH3: 50 V/ div.), (c) VS, IS, IL, IC waveform in steady-state (CH1: 50 V/ div., CH2: 5 A/ div., CH3: 2 A/ div., CH4: 2A/div.), and (d) VS, IS, Vd, IC waveform (CH1: 50V/div., CH2: 5 A/ div., CH3: 50 V/ div., CH4: 2A/ div.)                                                          |     |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

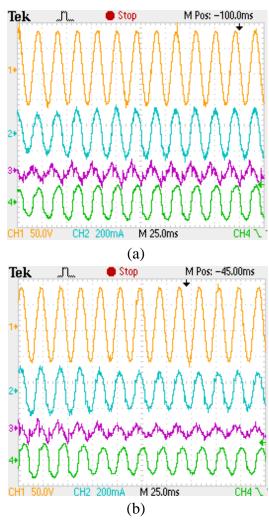

| Figure 4.23 | Experimental waveforms of CHB-MLI based SAPF with proposed controller under R-L loading (a) $V_S$ , $I_S$ , $I_L$ , $I_C$ waveform with step- increment of loading, and (b) $V_S$ , $I_S$ , $I_L$ , $I_C$ waveform with step- decrement of loading (CH1: $50V/div.$ , CH2: $200 \text{ mA/div.}$ ) | 127 |

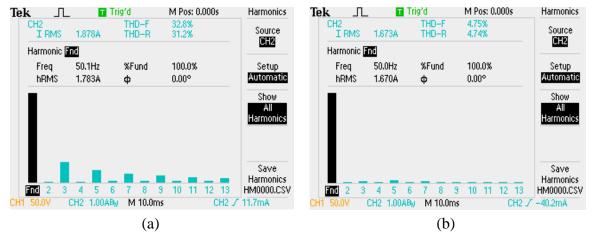

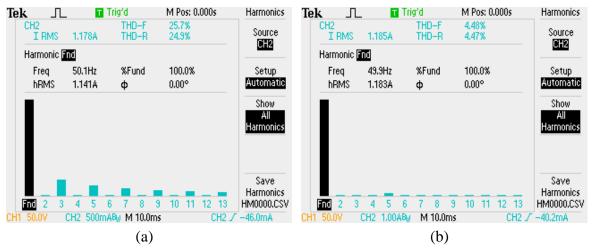

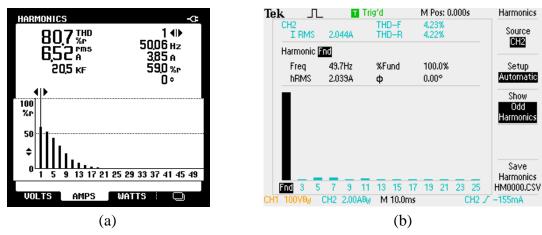

| Figure 4.24 | THD of source current with R-L loading (a) before compensation, and (b) after compensation                                                                                                                                                                                                         | 128 |

| Figure 4.25 | Performance of five-level CHB-MLI based SAPF with R-C loading (a) $V_S$ and non-linear $I_S$ , and (b) THD of $I_S$ before SAPF operation                                                                                                                                                          | 128 |

| Figure 4.26 | (a) VS, IS, IL and IC during steady-state condition, and (b) VS, IS, IC and MLI output waveform with R-C loading (CH1: 50V/div, CH2: 5 A/ div., CH3: 5 A/div.)                                                                                                                                     | 129 |

| Figure 4.27 | THD of I <sub>S</sub> after SAPF operation with R-C loading                                                                                                                                                                                                                                        | 129 |

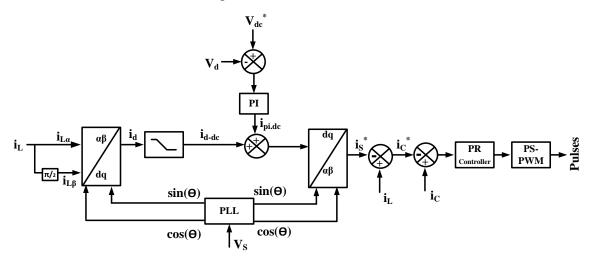

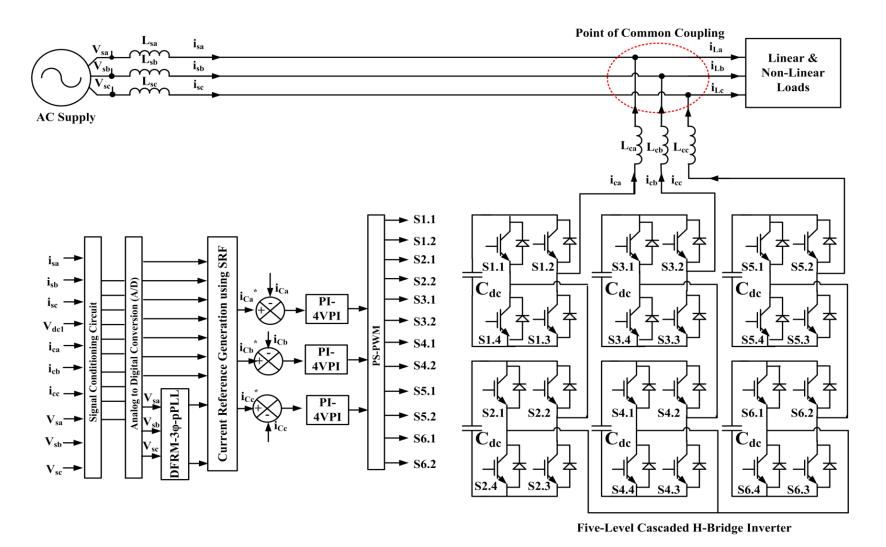

| Figure 5.1  | Implementation of five-level CHB-MLI based SAPF with proposed control algorithm                                                                                                                                                                                                                    | 135 |

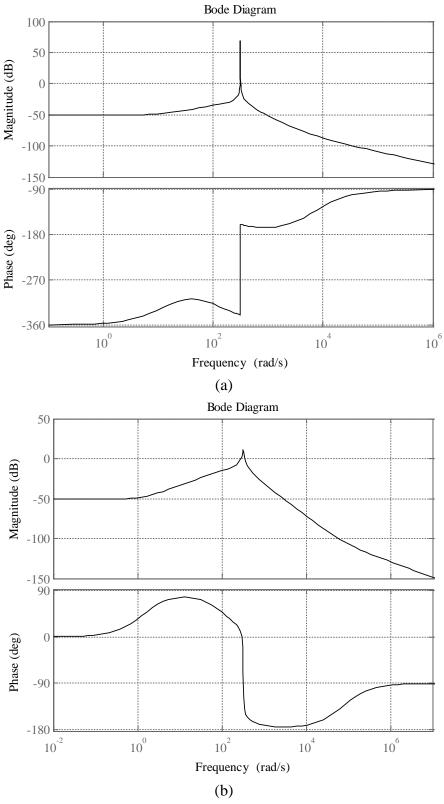

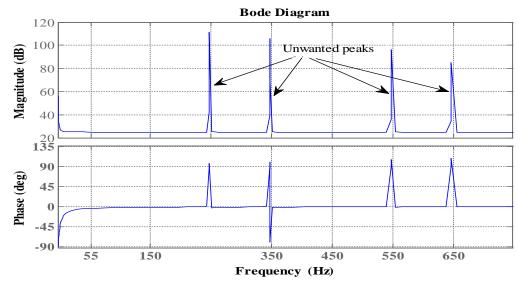

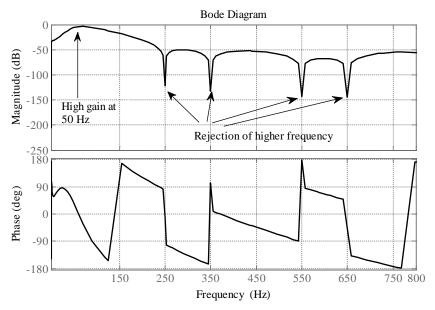

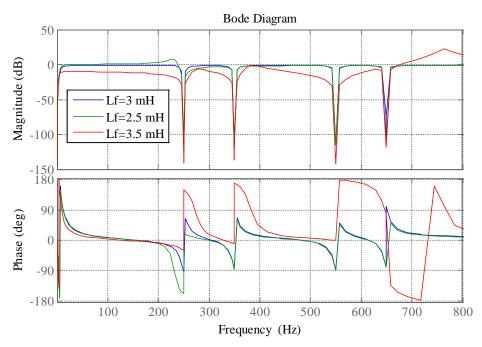

| Figure 5.2  | Bode-plot of PI-MR controller                                                                                                                                                                                                                                                                      | 137 |

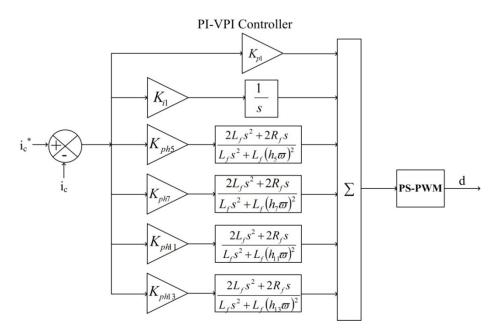

| Figure 5.3  | PI-VPI compensator applied to CHB-MLI based SAPF                                                                                                                                                                                                                                                   | 138 |

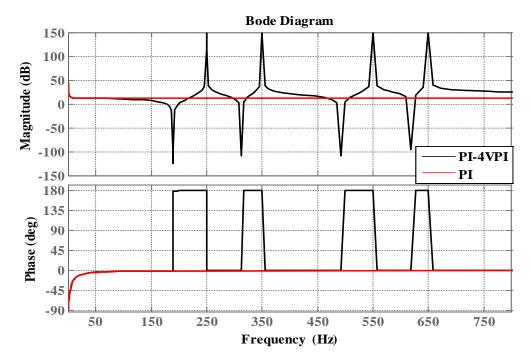

| Figure 5.4  | Open-loop response of PI-VPI compensator with respect to PI compensator                                                                                                                                                                                                                            | 139 |

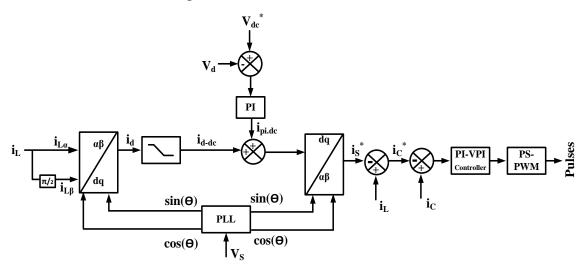

| Figure 5.5  | Current reference generation technique with proposed DFRM-three-phase-pPLL                                                                                                                                                                                                                         | 141 |

| Figure 5.6  | Closed-loop control of proposed SAPF control technique                                                                                                                                                                                                                                             | 142 |

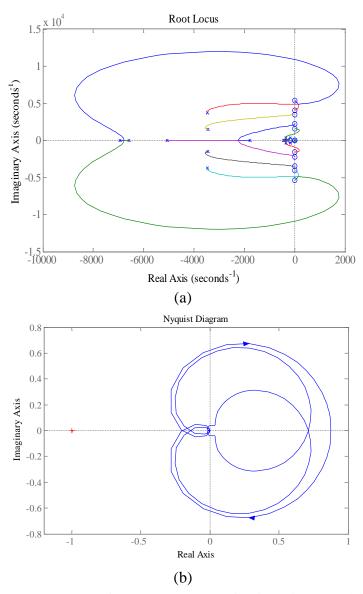

| Figure 5.7  | (a) Root-locus plot of closed-loop transfer function, and (b) nyquist plot of closed-loop transfer function             | 144 |

|-------------|-------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 5.8  | Bode-plot of closed-loop proposed controller transfer function                                                          | 145 |

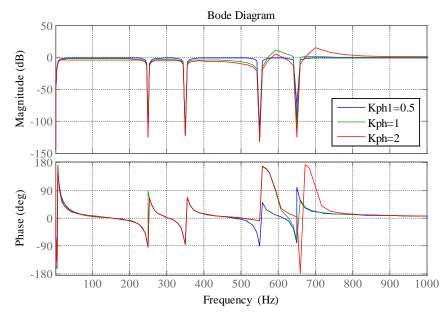

| Figure 5.9  | Bode-plot of closed-loop proposed controller transfer function with variation of gain parameters                        | 145 |

| Figure 5.10 | Bode-plot of closed-loop proposed current controller transfer function with variation of line impedance                 | 146 |

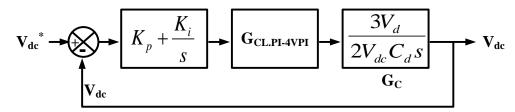

| Figure 5.11 | DC-link voltage control loop                                                                                            | 147 |

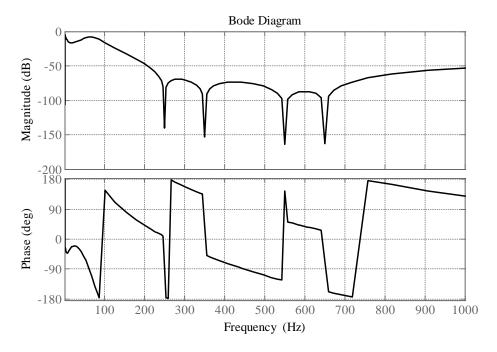

| Figure 5.12 | Bode-plot of closed-loop DC-link voltage control                                                                        | 147 |

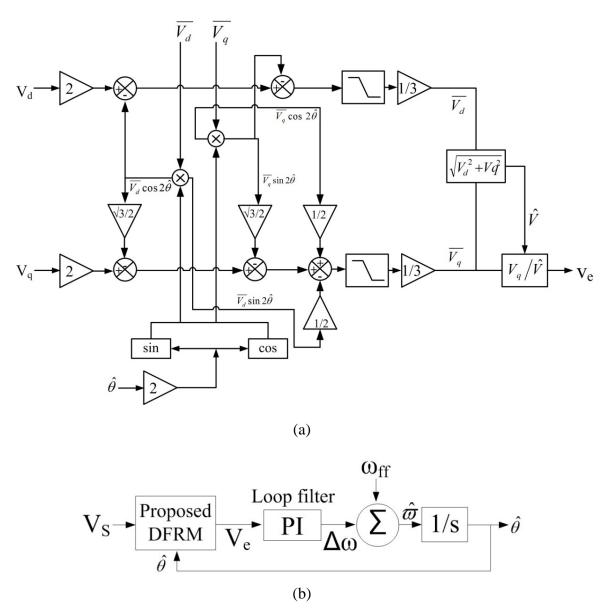

| Figure 5.13 | (a) DFRM-3 $\phi$ -pPLL structure, and (b) proposed PLL structure                                                       | 151 |

| Figure 5.14 | Particle swarm optimization algorithm                                                                                   | 154 |

| Figure 5.15 | Proposed methodology for finding out optimal solutions                                                                  | 156 |

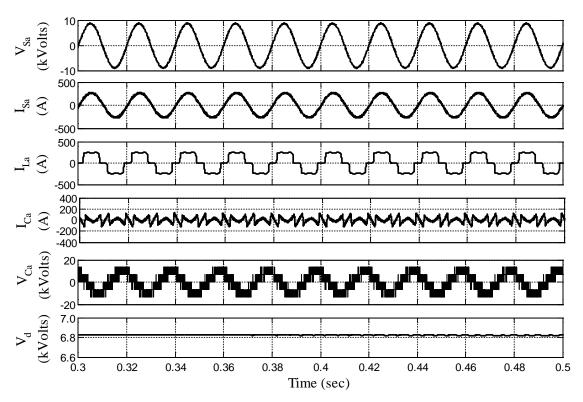

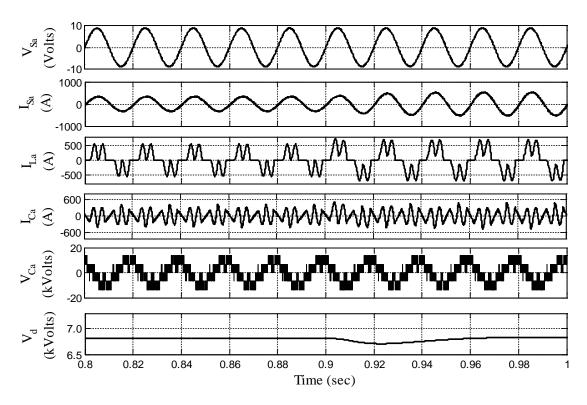

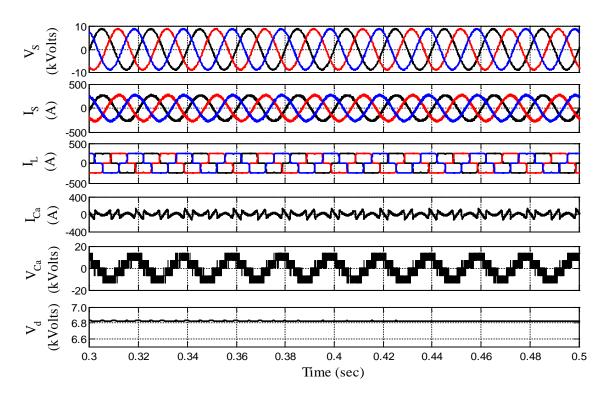

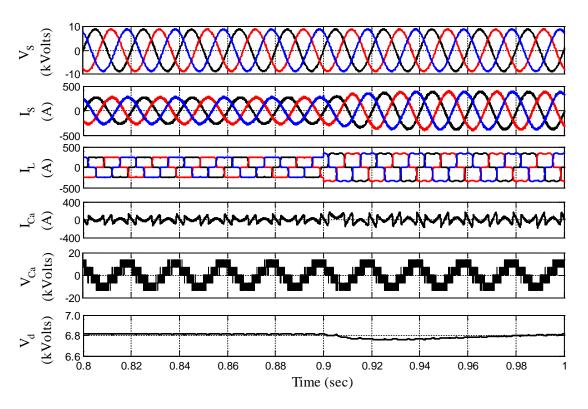

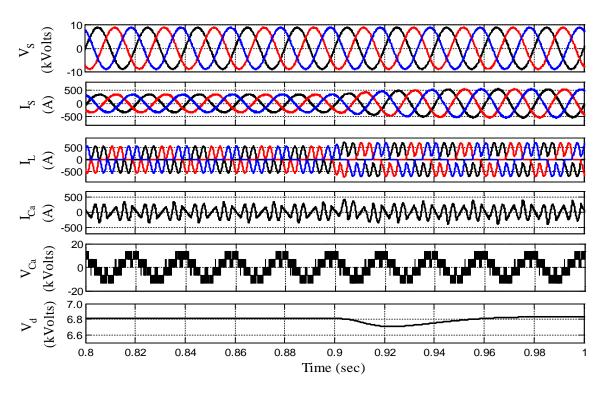

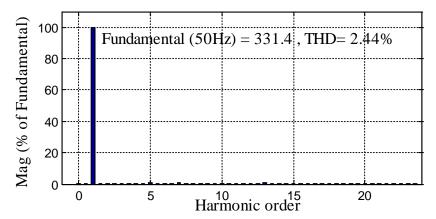

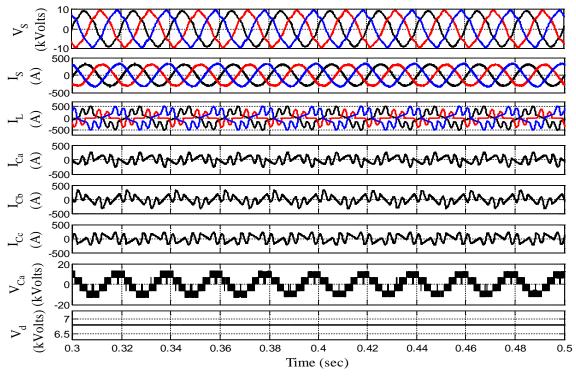

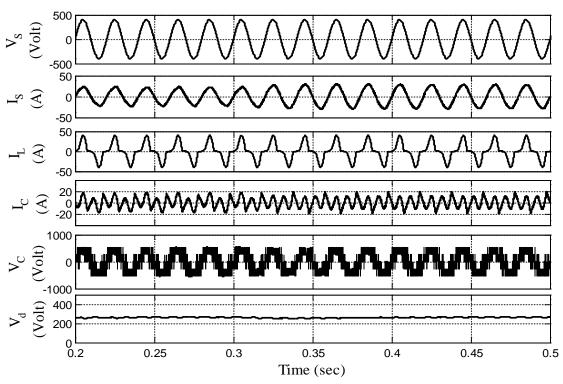

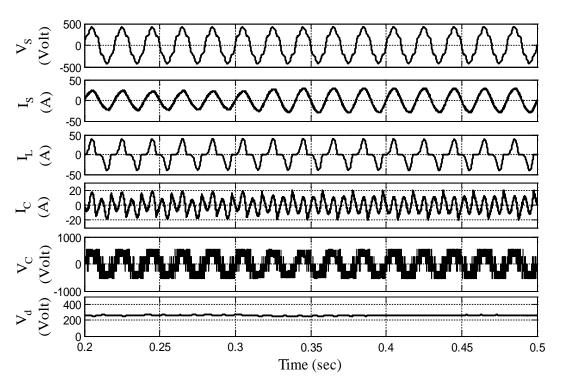

| Figure 5.16 | Steady-state performance of CHB-MLI based SAPF with proposed control strategy with R-L loading                          | 159 |

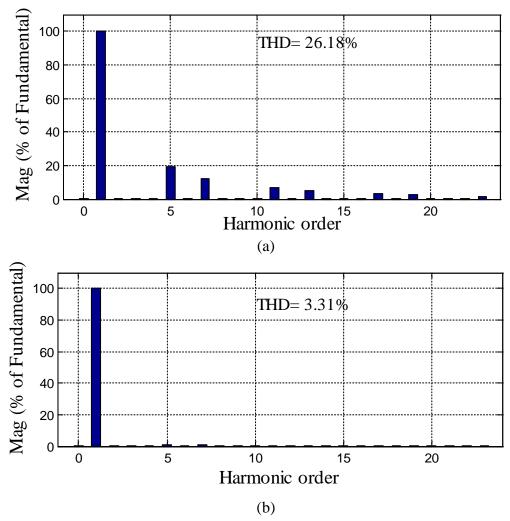

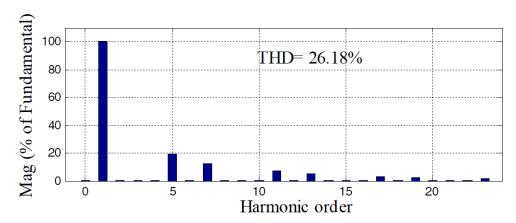

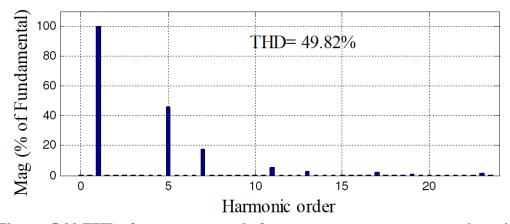

| Figure 5.17 | THD of source current before source current compensation with R-L loading                                               | 160 |

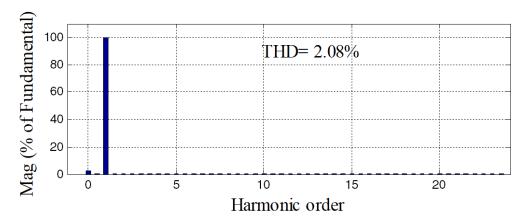

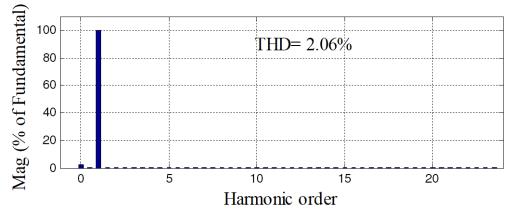

| Figure 5.18 | THD of source current after source current compensation with R-L loading                                                | 160 |

| Figure 5.19 | Transient-state performance of CHB-MLI based SAPF with proposed control strategy during load increment with R-L loading | 161 |

| Figure 5.20 | Transient-state performance of CHB-MLI based SAPF with proposed control strategy during load decrement with R-L loading | 161 |

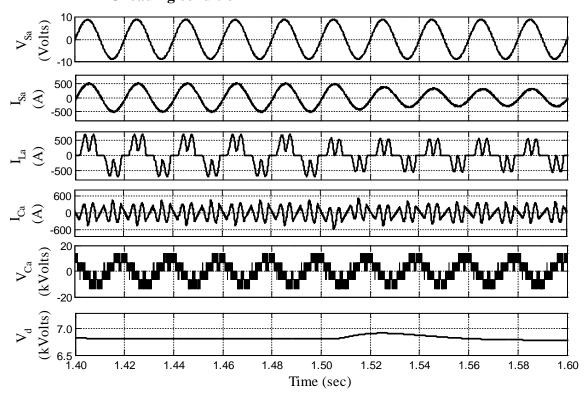

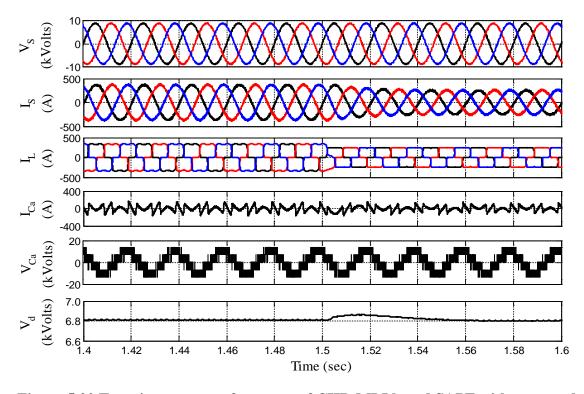

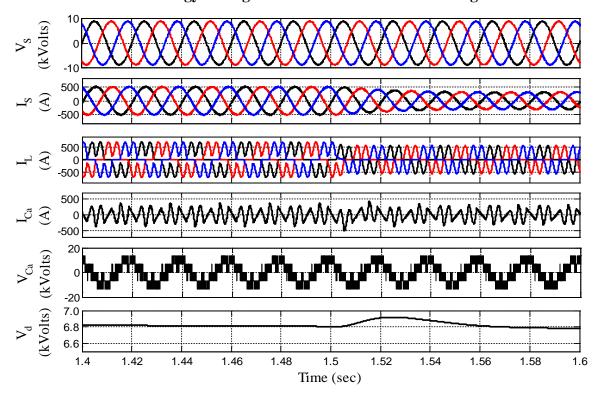

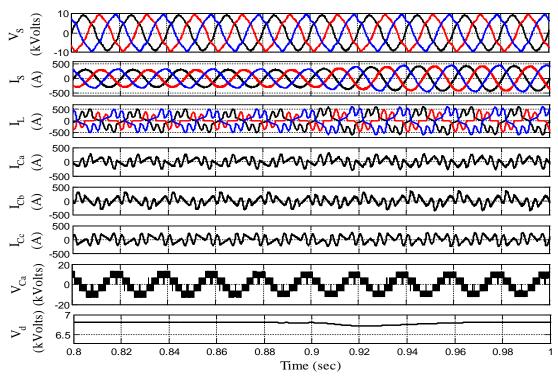

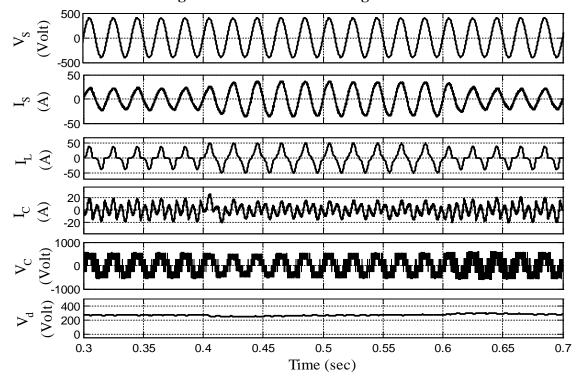

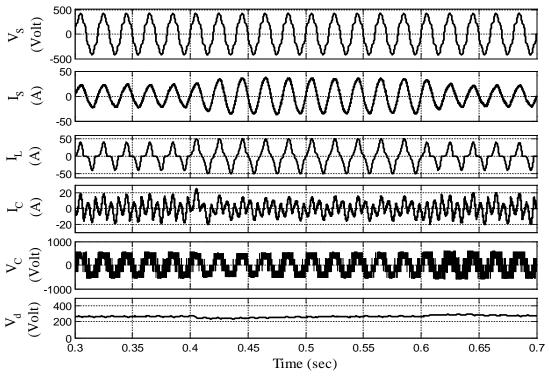

| Figure 5.21 | Steady-state performance of CHB-MLI based SAPF with proposed control strategy under R-C loading                         | 162 |

| Figure 5.22 | THD of source current before source current compensation with R-C loading                                                                                                                                                                   | 163 |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 5.23 | THD of source current after source current compensation with R-C loading                                                                                                                                                                    | 163 |

| Figure 5.24 | Transient-state performance of CHB-MLI based SAPF with proposed control strategy during load increment with R-C loading                                                                                                                     | 164 |

| Figure 5.25 | Transient-state performance of CHB-MLI based SAPF with proposed control strategy during load decrement with R-C loading condition                                                                                                           | 164 |

| Figure 5.26 | Proposed PI-VPI compensator based SRF control algorithm for single-phase CHB-MLI                                                                                                                                                            | 166 |

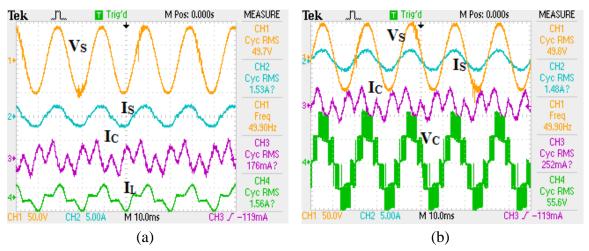

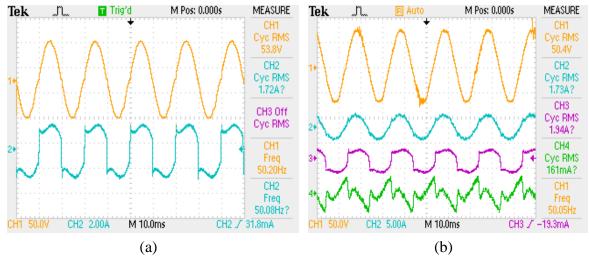

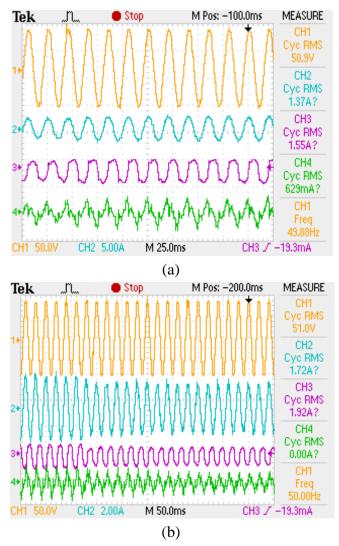

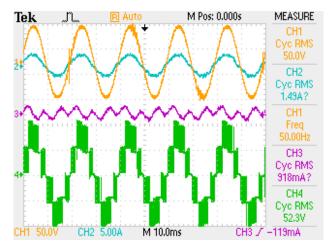

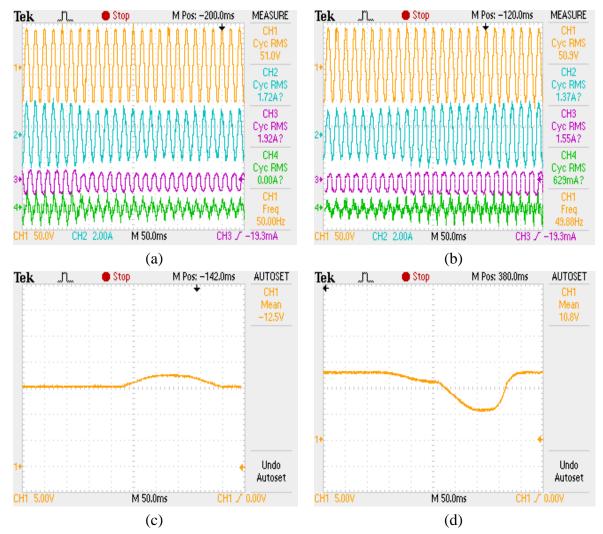

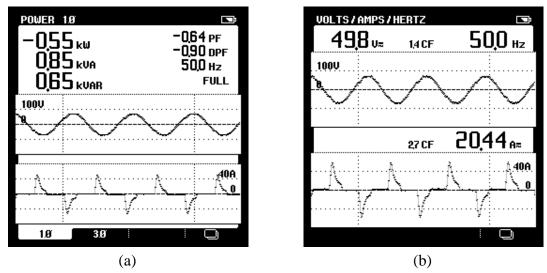

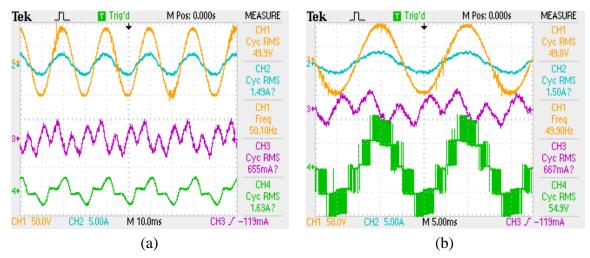

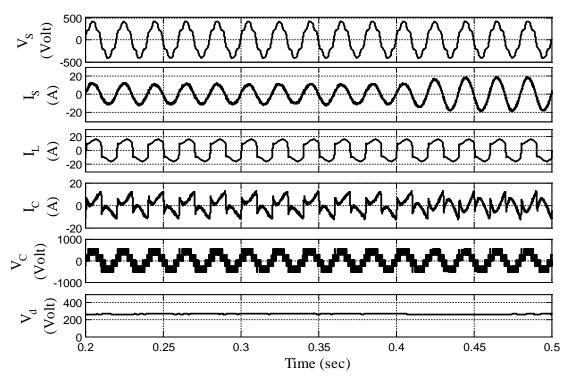

| Figure 5.27 | Steady-state performance of MLI based SAPF with proposed controller under R-L loading (a) VS with non-linear IS, and (b) VS, IS, IC, IL waveform after compensation (CH1: 50V/div., CH2: 2A/div., CH3: 5A/div., CH3: 5A/div., CH4: 5A/div.) | 167 |

| Figure 5.28 | Performance of MLI based SAPF with R-L loading (a) five-level MLI output voltage, and (b) $V_S$ , $I_S$ , $V_d$ , and $I_C$ steady-state waveform                                                                                           | 168 |

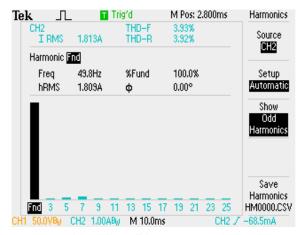

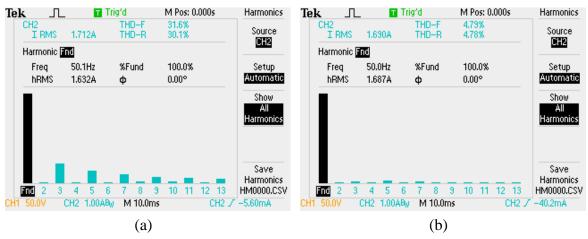

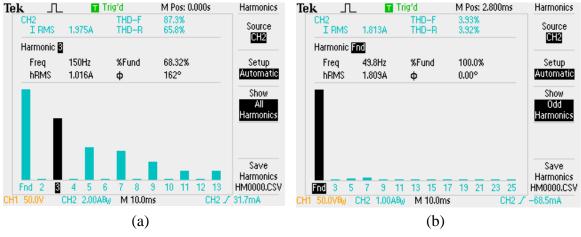

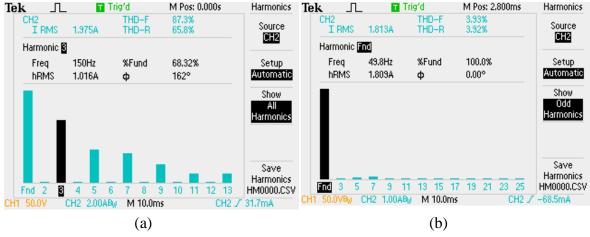

| Figure 5.29 | THD profile of source current with R-L loading condition (a) before compensation, and (b) after compensation                                                                                                                                | 168 |

| Figure 5.30 | Transient performance of CHB-MLI based SAPF with proposed controller under R-L loading condition (a) load increment, and (b) load decrement                                                                                                 | 169 |

| Figure 5.31 | Transient performance of CHB-MLI based SAPF during switching off condition                                                                                                                                                                  | 170 |

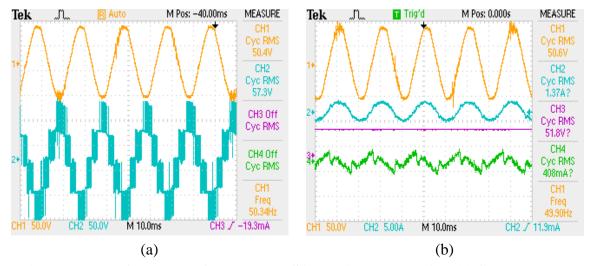

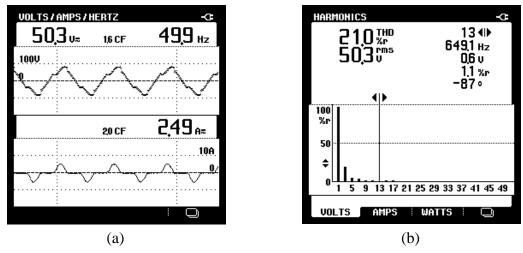

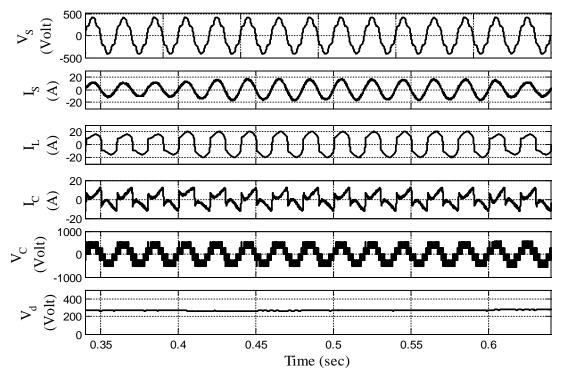

| Figure 5.32 | Steady-state performance of CHB-MLI based SAPF with                     | 170 |

|-------------|-------------------------------------------------------------------------|-----|

|             | proposed control algorithm under R-C loading condition (a)              |     |

|             | VS with non-linear IS, and (b) VS, IS, IC, and IL steady-state          |     |

|             | waveform (CH1: 50V/div., CH2: 5A/div., CH3: 5A/div.,                    |     |

|             | CH4: 5A/div.)                                                           |     |

| Figure 5.33 | Steady-state performance of MLI based SAPF including                    | 171 |

|             | inverter voltage with R-C loading                                       |     |

| Figure 5.34 | THD of source current under R-C loading condition (a) before            | 171 |

|             | compensation, and (b) after compensation                                |     |

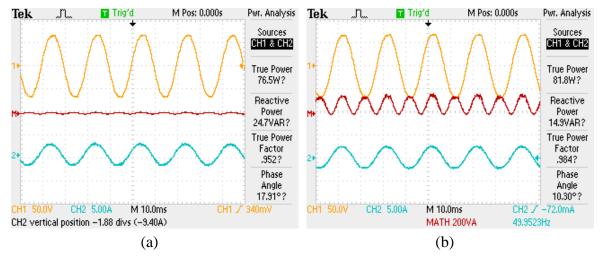

| Figure 5.35 | Performance comparison of proposed control algorithm with               | 172 |

|             | conventional control in terms of reactive power compensation            |     |

|             | with R-L load (a) power factor and reactive power with                  |     |

|             | conventional controller, and (b) power factor and reactive              |     |

|             | power with proposed controller                                          |     |

| Figure 5.36 | Performance comparison of proposed control algorithm with               | 173 |

|             | conventional control in terms of reactive power compensation            |     |

|             | with R-C load (a) power factor and reactive power with                  |     |

|             | conventional controller, and (b) power factor and reactive              |     |

|             | power with proposed controller                                          |     |

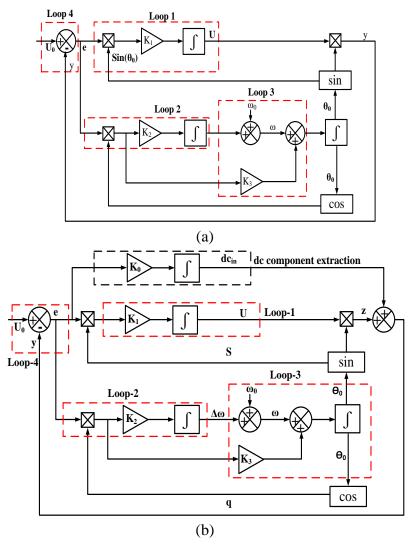

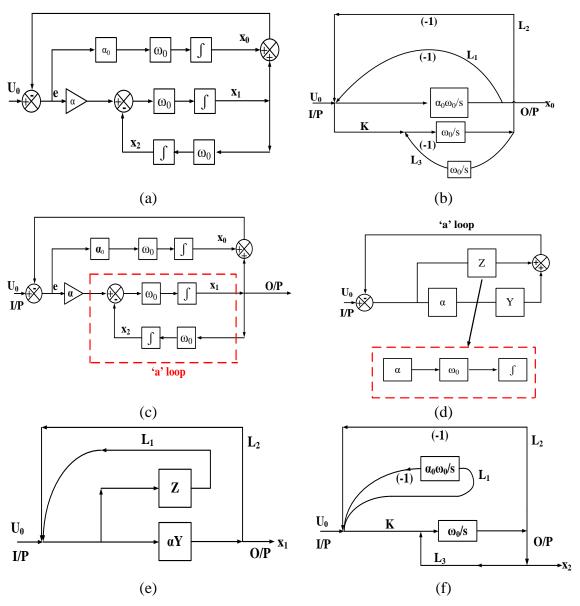

| Figure 6.1  | (a) E-PLL and (b) Advanced PLL                                          | 179 |

| Figure 6.2  | (a) SOGI based OSG diagram of advanced PLL, (b) loop                    | 184 |

|             | diagram for $X_0/U_0$ , (c) rearranged loop diagram for $X_0/U_0$ , (d) |     |

|             | simplified loop diagram for $X_0/U_0$ , (e) loop diagram for            |     |

|             | $X_1/U_0$ , and (f) loop diagram of $X_2/U_0$                           |     |

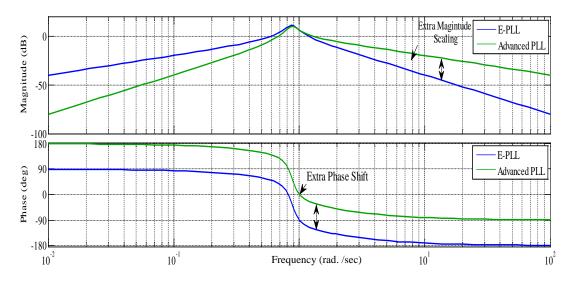

| Figure 6.3  | Bode plot comparison between E-PLL and advanced PLL                     | 187 |

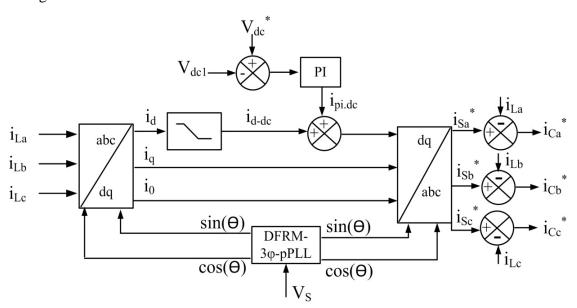

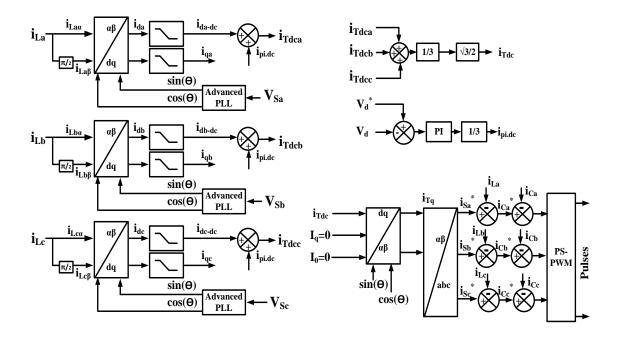

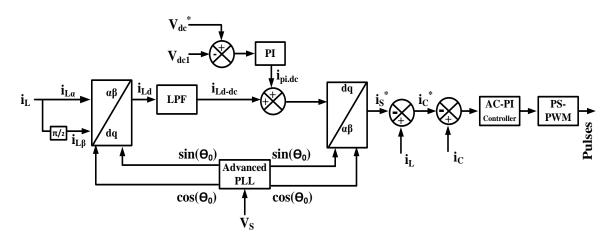

| Figure 6.4  | Control technique for five-level CHB-MLI based SAPF                     | 189 |

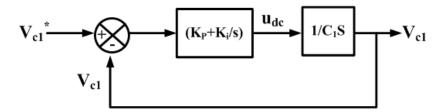

| Figure 6.5  | Closed-loop circuit of DC-link voltage control                          | 190 |

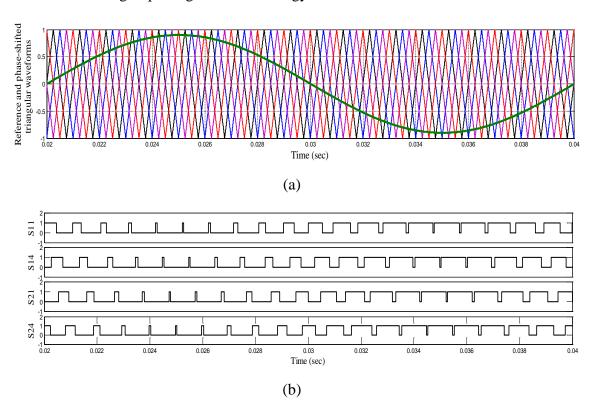

| Figure 6.6  | (a) PS-PWM technique, and (b) gate pulses for two H-bridges                                                                                                                                                    | 191 |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

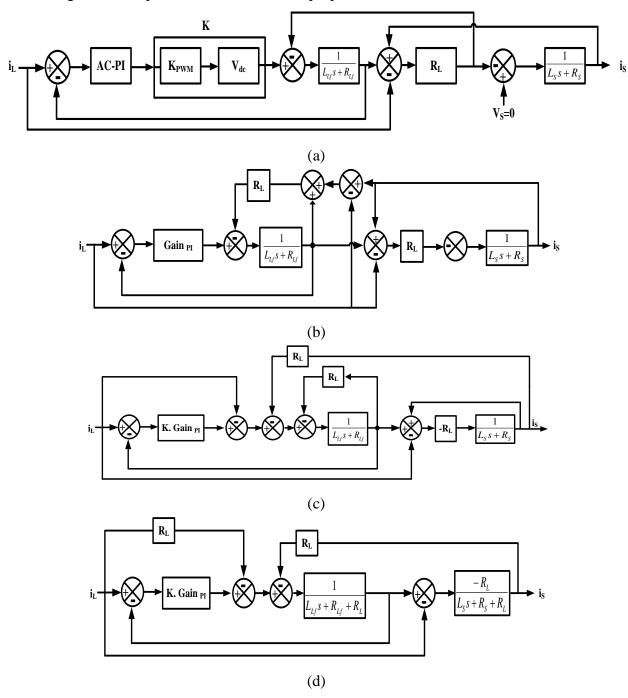

| Figure 6.7  | (a) Closed-loop transfer function of control algorithm, (b) equivalent loop diagram considering MLI and PWM gain parameters, (c) rearranged loop diagram, and (d) loop diagram using block reduction technique | 192 |

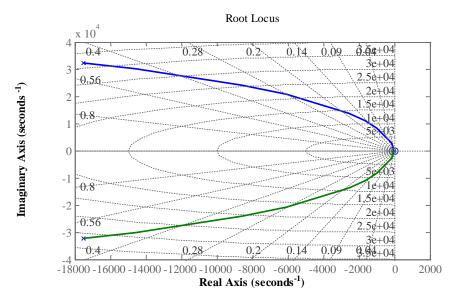

| Figure 6.8  | Root-locus diagram of closed-loop modified control for CHB-MLI based SAPF                                                                                                                                      | 193 |

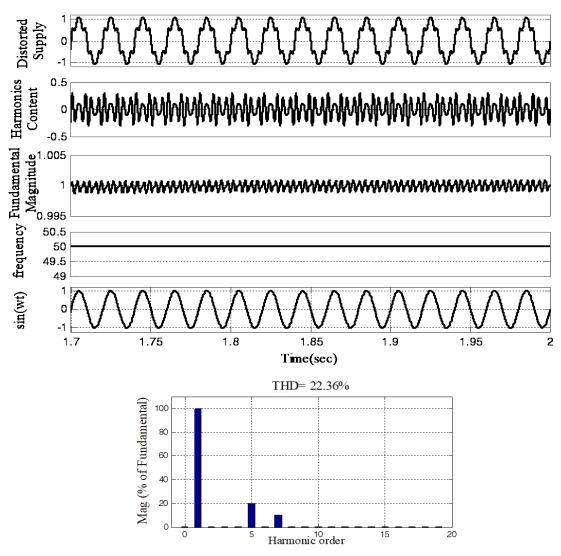

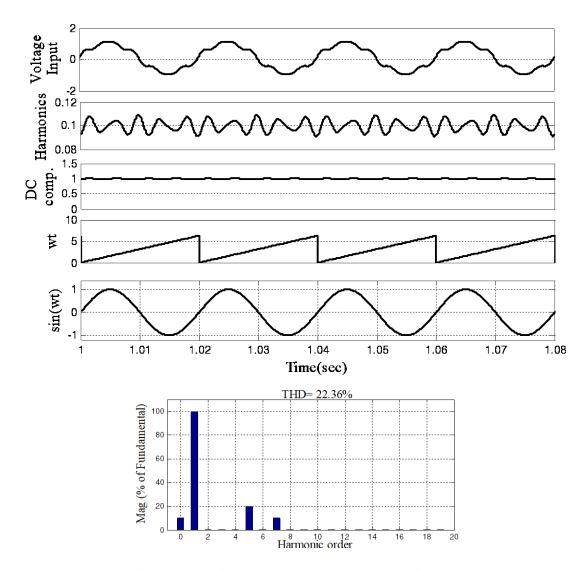

| Figure 6.9  | Performance of advanced PLL with harmonic injection                                                                                                                                                            | 194 |

| Figure 6.10 | Performance of advanced PLL with DC component and odd harmonic injection                                                                                                                                       | 195 |

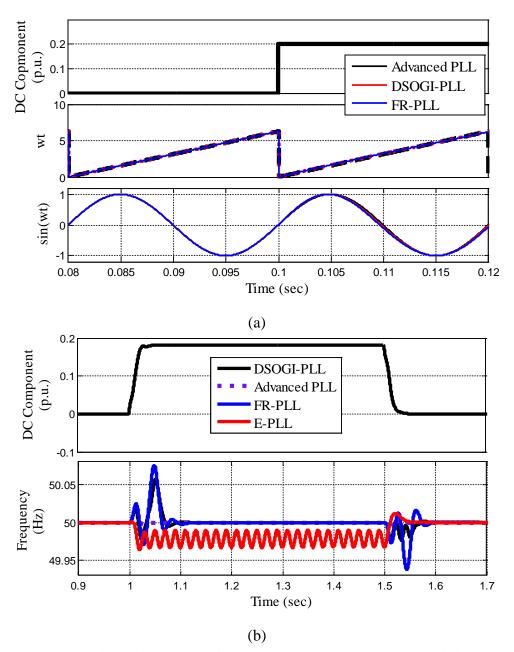

| Figure 6.11 | Dynamic performance of advanced PLL (a) with 20% dc injection, and (b) frequency response application and removal of dc component                                                                              | 196 |

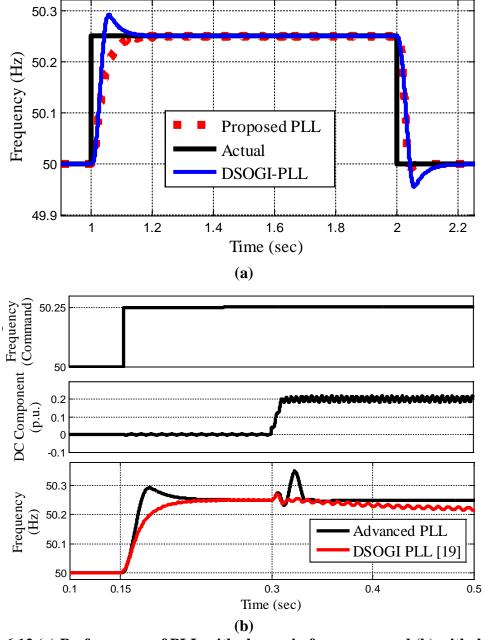

| Figure 6.12 | (a) Performance of PLL with change in frequency, and (b) with dc component and change in frequency                                                                                                             | 197 |

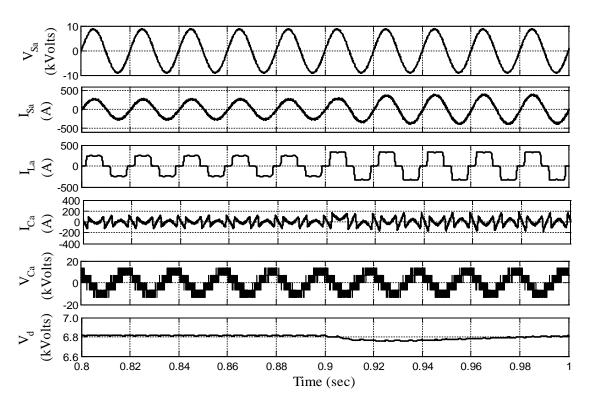

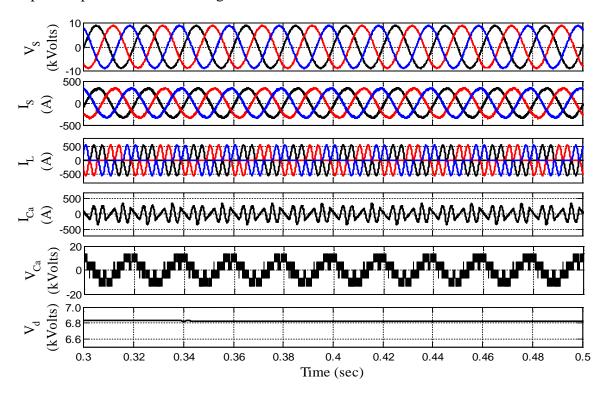

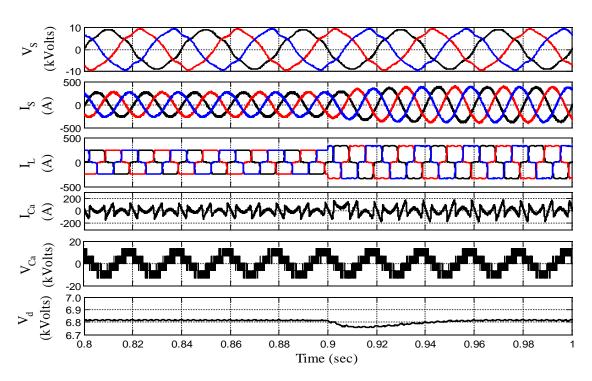

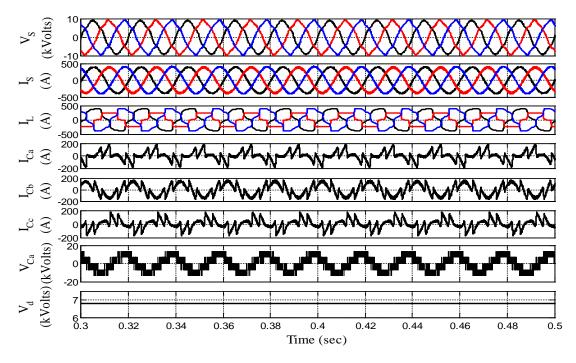

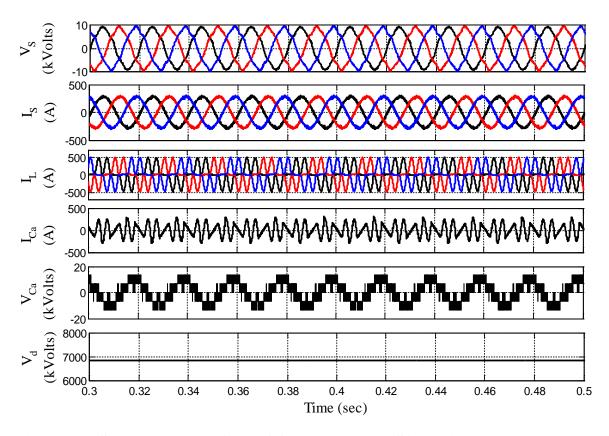

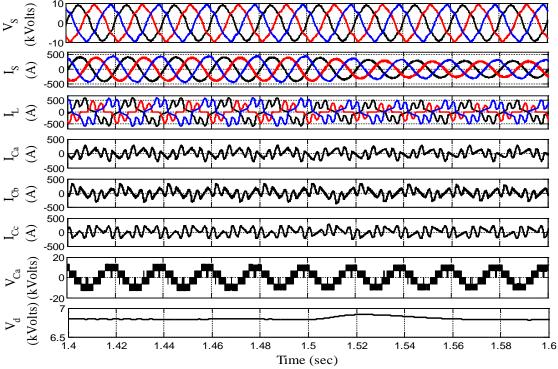

| Figure 6.13 | Steady-state waveform of CHB-MLI bases SAPF with proposed control algorithm under distorted source voltage and balanced R-L loading                                                                            | 199 |

| Figure 6.14 | Transient response of CHB-MLI based SAPF with proposed control algorithm with load increment under distorted source voltage and balanced R-L loading                                                           | 200 |

| Figure 6.15 | Transient response of CHB-MLI based SAPF with proposed control algorithm with load decrement under distorted source voltage and balanced R-L loading                                                           | 200 |

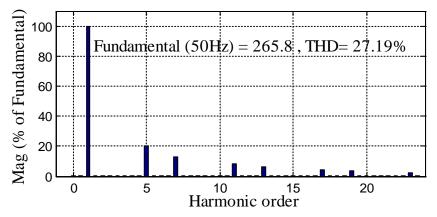

| Figure 6.16 | THD profile of source current before compensation for R-L loading                                                                                                                                              | 201 |

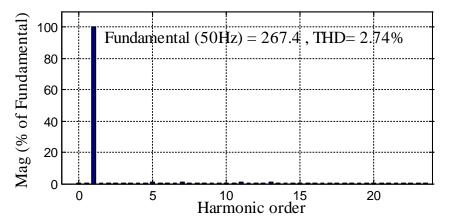

| Figure 6.17 | THD profile of source current after compensation for R-L                                                                                                                                                       | 201 |

## loading

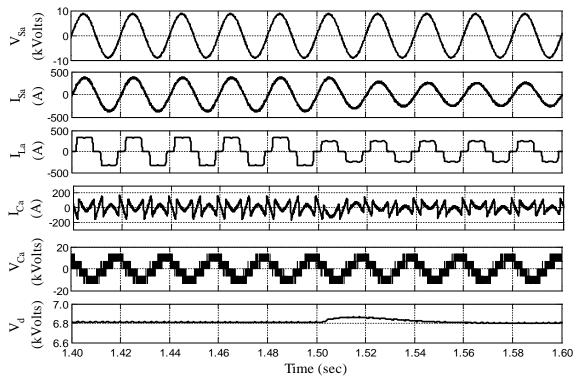

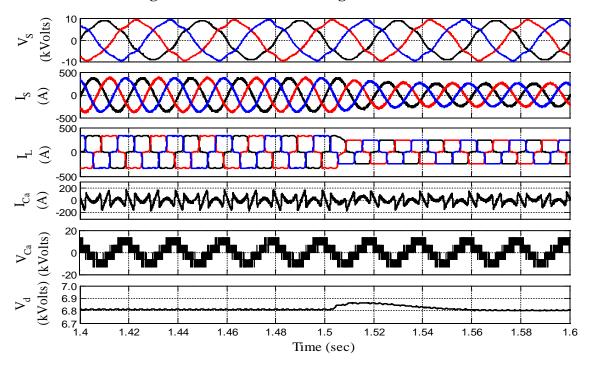

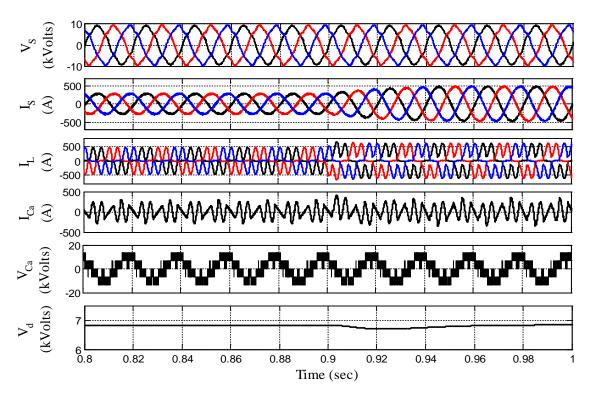

| Figure 6.18 | Steady-state waveform of CHB-MLI bases SAPF with proposed control algorithm under distorted source voltage and unbalanced R-L loading                                     | 202 |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 6.19 | Transient response of CHB-MLI based SAPF with proposed control algorithm with load increment under distorted source voltage and unbalanced R-L loading                    | 203 |

| Figure 6.20 | Transient response of CHB-MLI based SAPF with proposed control algorithm with load decrement under distorted source voltage and unbalanced R-L loading                    | 203 |

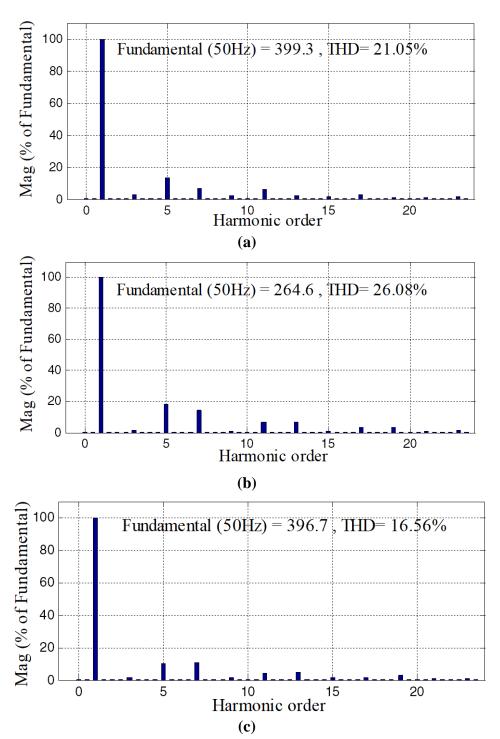

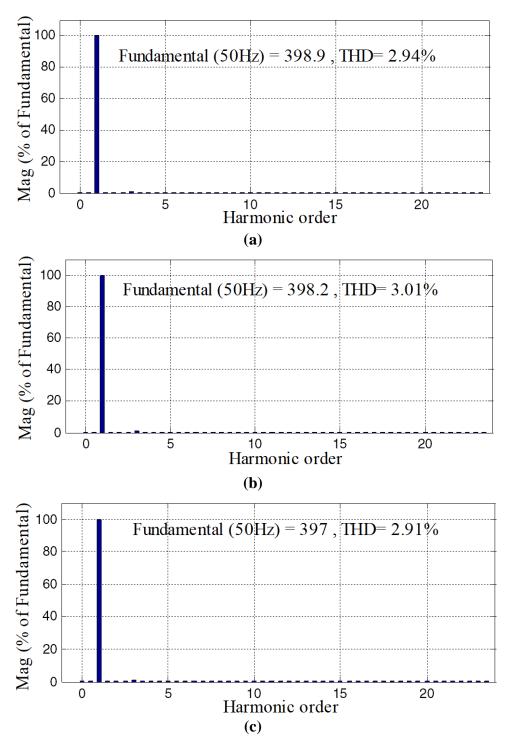

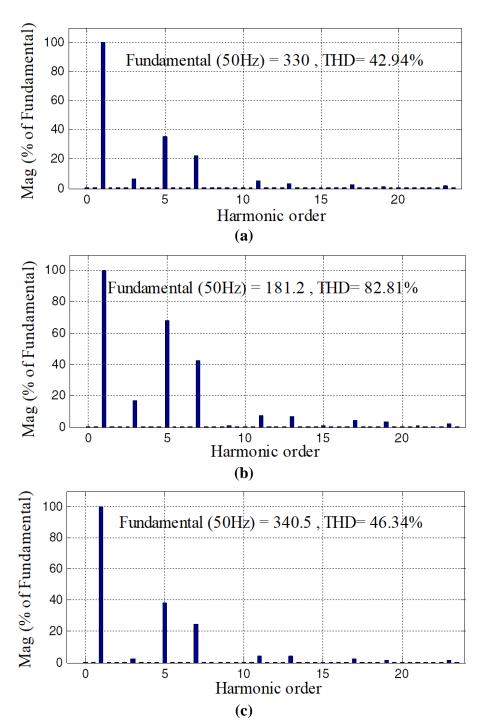

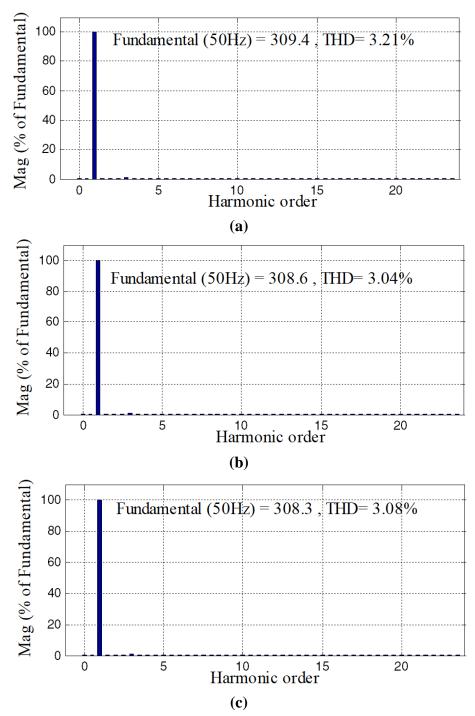

| Figure 6.21 | THD profile of source current before compensation for unbalanced R-L loading (a) THD profile of Phase 'A', (b) THD profile of Phase 'B', and (c) THD profile of Phase 'C' | 204 |

| Figure 6.22 | THD profile of source current after compensation for unbalanced R-L loading (a) THD profile of Phase 'A', (b) THD profile of Phase 'B', and (c) THD profile of Phase 'C'  | 205 |

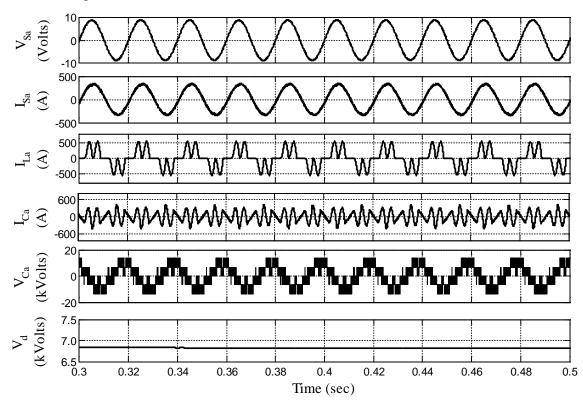

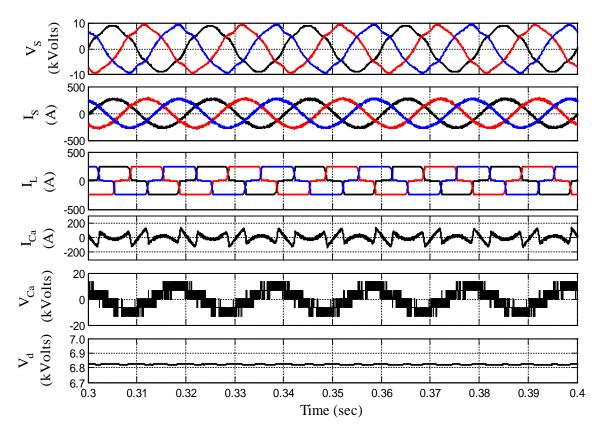

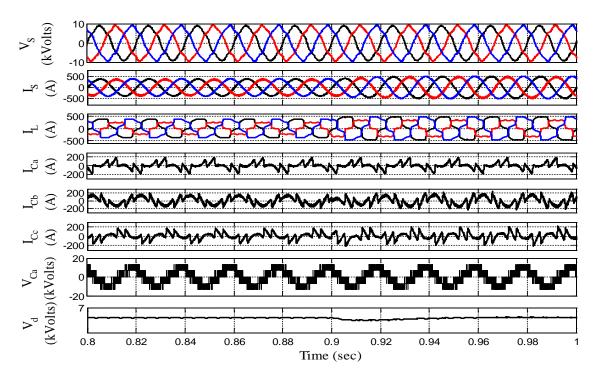

| Figure 6.23 | Steady-state waveform of CHB-MLI bases SAPF with proposed control algorithm under distorted source voltage and balanced R-C loading condition                             | 207 |

| Figure 6.24 | Transient response of CHB-MLI based SAPF with proposed control algorithm with load increment under distorted source voltage and balanced R-C loading                      | 208 |

| Figure 6.25 | Transient response of CHB-MLI based SAPF with proposed control algorithm with load decrement under distorted source voltage and balanced R-C loading                      | 208 |

| Figure 6.26 | THD profile of source current before compensation for R-C loading                                                                                                         | 209 |

| Figure 6.27 | THD profile of source current after compensation for R-C loading                                                                                                                                                                                                                                          | 209 |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

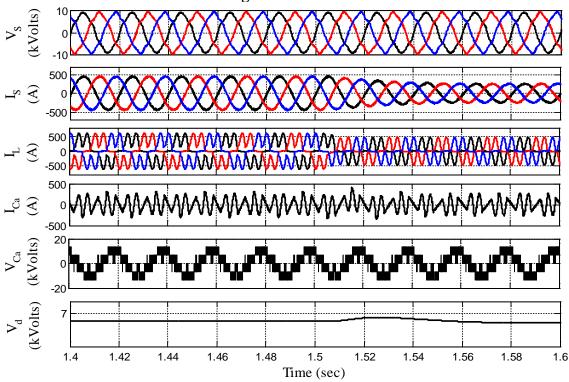

| Figure 6.28 | Steady-state waveform of CHB-MLI bases SAPF with proposed control algorithm under distorted source voltage and unbalanced R-C loading                                                                                                                                                                     | 210 |

| Figure 6.29 | Transient response of CHB-MLI based SAPF with proposed control algorithm with load increment under distorted source voltage and unbalanced R-C loading                                                                                                                                                    | 211 |

| Figure 6.30 | Transient response of CHB-MLI based SAPF with proposed control algorithm with load decrement under distorted source voltage and unbalanced R-C loading                                                                                                                                                    | 211 |

| Figure 6.31 | THD profile of IS before compensation (a)THD profile of Phase 'A' (b) THD profile of Phase 'B' and (c) THD profile of Phase 'C'                                                                                                                                                                           | 212 |

| Figure 6.32 | THD profile of IS before compensation (a)THD profile of Phase 'A' (b) THD profile of Phase 'B' and (c) THD profile of Phase 'C'                                                                                                                                                                           | 213 |

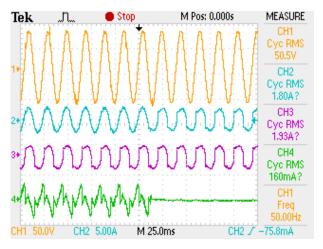

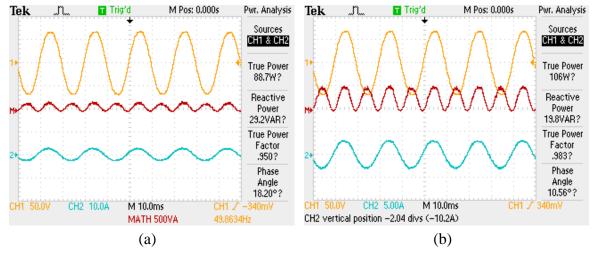

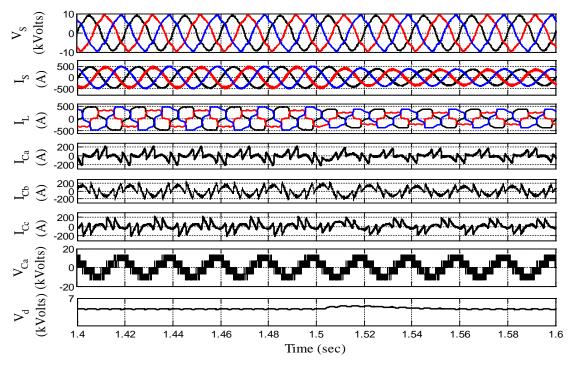

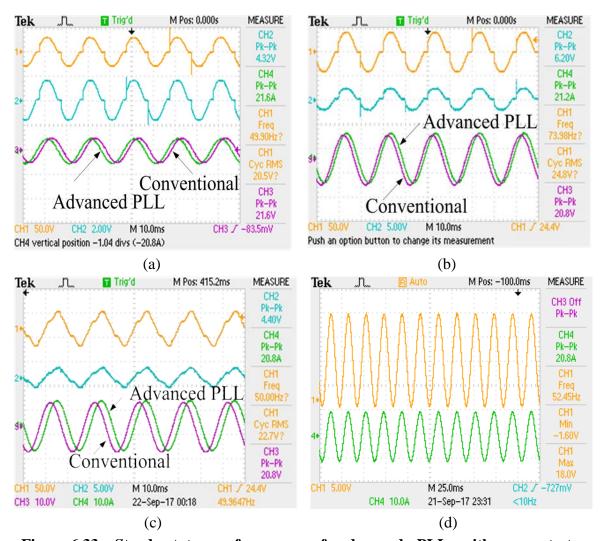

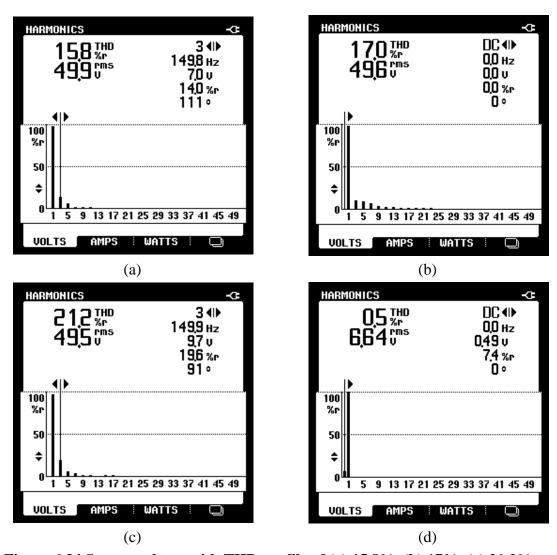

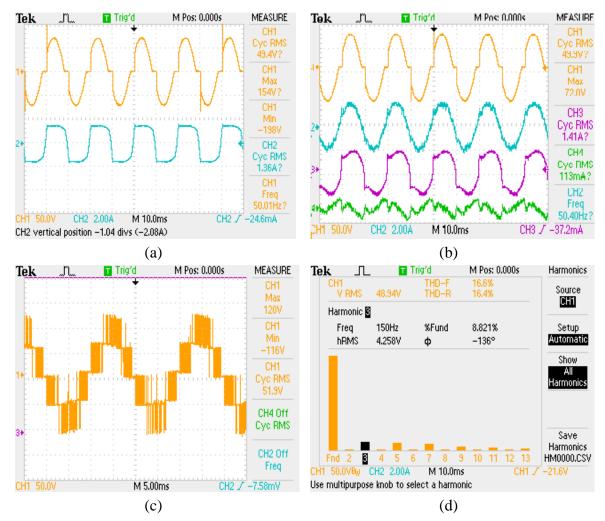

| Figure 6.33 | Steady-state performance of advanced PLL with respect to conventional PLL in distorted source voltage condition with (a) 15.8% THD, (b) 17% THD, (c) 21.2% THD, and (d) dc component                                                                                                                      | 215 |

| Figure 6.34 | Source voltage with THD profile of (a) 15.8%, (b) 17%, (c) 21.2%, and (d) 0.5% dc                                                                                                                                                                                                                         | 216 |

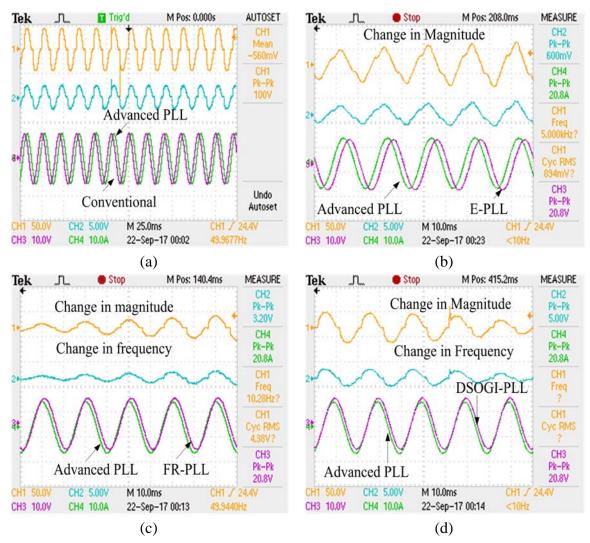

| Figure 6.35 | Performance of PLL in steady-state and transient conditions  (a) steady-state performance with dc injected source voltage,  (b) transient behavior with change in amplitude in presence,  (c) transient behavior with increment in amplitude and  frequency, and (d) transient behavior with decrement in | 217 |

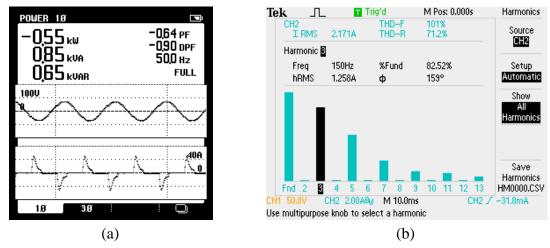

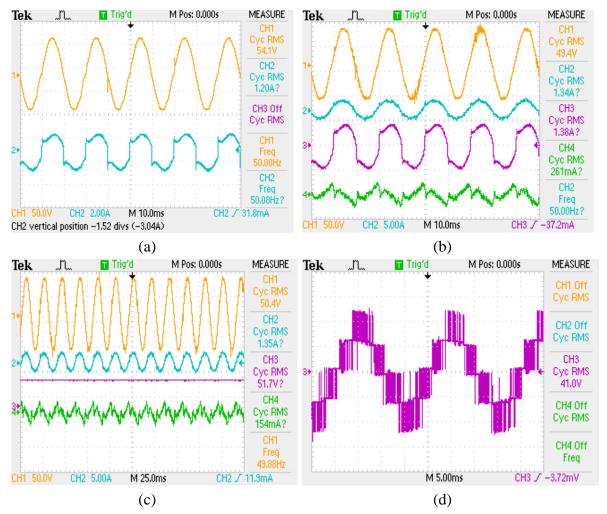

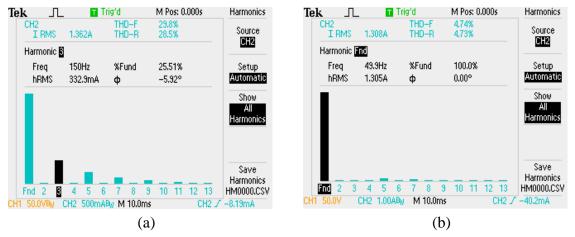

## amplitude