Α

Ph.D. Thesis

on

## Design of Highly Adaptive and Fault-tolerant Routing for Networks-on-Chip

## submitted as a partial fulfillment of Ph.D. program

in

Engineering

Place: Jaipur

Date: January 2, 2017

#### Department of Computer Science and Engineering

Malaviya National Institute of Technology , Jaipur - 302017

### Certificate

We hereby certify that the Thesis titled, "Design of Highly Adaptive and Fault-tolerant Routing for Networks-on-Chip" submitted by Manoj Kumar (2011RCP7126) is the research work done under our supervision, thus is accepted and finalized for submission in partial fulfillment of Ph.D. Program.

Place: Jaipur

Supervisor(s):

Manoj Singh Gaur, (Professor)

Date: January 2, 2017 Vijay Laxmi, (Associate Professor)

### DECLARATION

I, Manoj Kumar, declare that I own the research work introduced in this Thesis titled, "Design of Highly Adaptive and Fault-tolerant Routing for Networks-on-Chip" and the research contents used in this thesis. I with this assure that:

- The research work produced in this thesis is for the partial fulfillment of the degree of "*Doctor of Philosophy*" at MNIT, Jaipur.

- I have stated all the major resources used for the help.

- Where I have used proper citation for the work proposed by other researchers and quoted the source. This entire thesis belongs to me with the some exception of such citations.

- Where I have taken references of previously published work of my co-authors and other researchers and this is always clearly attributed.

- I have clearly stated any part of this Thesis that has been previously submitted for a degree or any other qualification at MNIT or any other institution.

Signed:

Date:

#### **ACKNOWLEDGEMENT**

It was a matter great pleasure for me to enroll for Ph.D. program in the Department of Computer Science and Engineering, Malaviya National Institute of Technology, Jaipur, India. I would like to express sincere thanks and appreciation to my Ph.D. supervisors Dr. Manoj Singh Gaur and Dr. Vijay Laxmi. I am also thankful to Dr. Seok-bum Ko (Professor, University of Saskatchewan, Canada) and Dr. Masoud Daneshtalab (Associate Professor, University of Mlardalen, Sweden) for their continuous technical/non-technical support. They have devoted valuable time to guide me. Their suggestions and cooperation together with the motivation have made it possible to complete my research work. They have provided me a good atmosphere for doing work peacefully as well as resourcefully.

I am also grateful to Dr. Parvez Faruki (Lecturer, Polytechnic College, Bhavnagar, Gujrat) for his continuous motivation during Ph.D. duration.

I convey special thanks to my DREC committee members Dr. Dinesh Gopalani (MNIT, Jaipur), Dr. Girdhari Singh (MNIT, Jaipur) and Dr. Lava Bhargava (MNIT, Jaipur) for their inspiration and encouragement that directed me toward the completion of this research.

My special thanks to my wonderful friends and fellow researchers, Smita, Rimpy, Anil, Gaurav, Sonal, Ashish for revitalizing each day. From the depth of my heart, I acknowledge all those persons who have motivated me to complete the thesis. I also express my apology that I couldn't mention them in person.

Finally, at the end, I would like to thank God, the Creator of the Earth, the Almighty. The Supreme in power and knowledge and the most merciful, Whom I acquired guidance and knowledge to do something beneficial for the humanity.

Dedications

This Thesis is Dedicated to my wife **Mahima**, who was always with me to motivate for the work and my Kids **Cheena and Cherry**, who were always ready to play with me to make me fresh.

#### ABSTRACT

Network-on-Chip (NoC) has emerged as a promising alternative to traditional bus-based architectures for inter-core communication. It has also been accepted commercially as the communication paradigm for Systems-on-Chip (SoC), instead of dedicated wires or shared buses. The overall NoC performance depends on many parameters such as topology, flow control, routing schemes, task mapping, quality-of-service and switching methods. In all cases, the *degree of adaptiveness* has a significant effect on the overall performance of any adaptive routing algorithm. In addition, *fault tolerance* is the another aspect related to the reliability of NoCs. The objective of this thesis is to design and develop turn models for routing algorithms that provide high degree of adaptiveness and/or fault tolerance to improve the overall performance of the network.

Most of the routing algorithms proposed in the recent literature achieve deadlock-freedom by forcibly restricting certain routing turns so that the channel dependency graph remains acyclic. This requirement for the deadlock-freedom makes these algorithms more restrictive, thus reduces the degree of adaptiveness. The proposed algorithm enhances the functionality (routing turns) in virtual channels of existing algorithms to achieve high degree of adaptiveness for 2D mesh with wormhole switching. We have extended the aforementioned 2D turn model for three dimensions (3D) to achieve high adaptivity. The 3D turn model uses one, two and two virtual channels in X, Y and Z dimensions, respectively. We have also developed a highly adaptive and fault-tolerant routing algorithm for 2D mesh topology. The proposed algorithm can handle single link faults. It can also handle multiple link faults if fault's boundary do not overlap with each other. We have designed another fault-tolerant routing algorithm for 2D mesh topology. The proposed algorithm is able to handle single link faults, and it uses LBDR as its implementation.

# Contents

| Li       | st of            | Figur  | es          |                                                   | i  |

|----------|------------------|--------|-------------|---------------------------------------------------|----|

| Li       | List of Tables i |        |             | iv                                                |    |

| 1        | Intr             | oduct  | ion         |                                                   | 1  |

|          | 1.1              | Routi  | ng Overvie  | 2W                                                | 2  |

|          | 1.2              | Motiv  | ations      |                                                   | 3  |

|          | 1.3              | Objec  | tives       |                                                   | 6  |

|          | 1.4              | Contr  | ibutions of | f the Thesis                                      | 6  |

|          | 1.5              | Thesis | Outline .   |                                                   | 7  |

| <b>2</b> | Net              | works  | on-Chip     | (NoCs)                                            | 8  |

|          | 2.1              | Why I  | NoC: Evol   | ution of On-chip Communication Architectures      | 9  |

|          | 2.2              | NoC 7  | Topologies  |                                                   | 13 |

|          |                  | 2.2.1  | Direct T    | opologies                                         | 14 |

|          |                  | 2.2.2  | Indirect    | Topologies                                        | 15 |

|          | 2.3              | NoC I  | Router: Ge  | eneric Architecture                               | 18 |

|          | 2.4              | Switch | ning Meth   | ods                                               | 20 |

|          |                  | 2.4.1  | Circuit S   | Switching                                         | 21 |

|          |                  | 2.4.2  | Store-and   | d-Forward Switching                               | 22 |

|          |                  | 2.4.3  | Virtual (   | Cut-Through Switching                             | 23 |

|          |                  | 2.4.4  | Wormho      | le Switching                                      | 25 |

|          | 2.5              | Routi  | ng Algorit  | hms                                               | 25 |

|          |                  | 2.5.1  | Deadlock    | s in Routing                                      | 26 |

|          |                  | 2.5.2  | Livelocks   | s in Routing                                      | 27 |

|          |                  | 2.5.3  | Classifica  | ation of Routing Algorithms                       | 28 |

|          |                  |        | 2.5.3.1     | Source vs. Distributed Routing                    | 29 |

|          |                  |        | 2.5.3.2     | Unicast vs. Broadcast vs. Multicast Routing       | 30 |

|          |                  |        | 2.5.3.3     | Deterministic vs. Adaptive routing                | 30 |

|          |                  |        | 2.5.3.4     | Minimal vs. Non-minimal Routing                   | 31 |

|          |                  |        | 2.5.3.5     | Congestion-aware vs. Congestion-oblivious Routing | 31 |

|          |                  |        | 2.5.3.6     | Topology Dependent vs. Topology Independent       |    |

|          |                  |        |             | Routing                                           | 32 |

|          | 2.6              | Turn I | Model bas   | ed Routing Algorithms                             | 32 |

|          |                  | 2.6.1  | Partially   | Adaptive Algorithms                               | 33 |

|          |                   | 2.6.2 Fully Adaptive Algorithms                                                                                                             |   |

|----------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------|---|

|          | 2.7               | Recent Research Works and Issues                                                                                                            |   |

| 3        | 2D-               | CHARM: Congestion-aware and Highly Adaptive Routing Method                                                                                  | ł |

|          | for               | D-Mesh 47                                                                                                                                   |   |

|          | 3.1               | Overview                                                                                                                                    |   |

|          |                   | 3.1.1 Motivation and Background                                                                                                             |   |

|          |                   | 3.1.2 Mad- $y$ Turn Model                                                                                                                   |   |

|          |                   | 3.1.3 LEAR and HARAQ Turn Models                                                                                                            |   |

|          | 3.2               | Proposed Work                                                                                                                               |   |

|          |                   | 3.2.1 2D-CHARM: Turn Model                                                                                                                  |   |

|          |                   | 3.2.2 2D-CHARM: Routing Algorithm                                                                                                           |   |

|          |                   | 3.2.3 Deadlock Freedom of 2D-CHARM                                                                                                          |   |

|          |                   | 3.2.4 Livelock Freedom of 2D-CHARM                                                                                                          |   |

|          | 3.3               | Results Analysis                                                                                                                            |   |

|          |                   | 3.3.1 Uniform Traffic Pattern                                                                                                               |   |

|          |                   | 3.3.2 Non-uniform Traffic Patterns                                                                                                          |   |

|          |                   | 3.3.3 Application Traffic                                                                                                                   |   |

|          |                   | 3.3.4 Power Analysis                                                                                                                        |   |

|          |                   | 3.3.5 Area Analysis                                                                                                                         |   |

|          | 3.4               | Inferences                                                                                                                                  |   |

| 4        | 9D                | CHARM: Adaptive Routing Method for 3D-Mesh 78                                                                                               |   |

| 4        | <b>3D-</b><br>4.1 | CHARM: Adaptive Routing Method for 3D-Mesh78Overview78                                                                                      |   |

|          | 4.1<br>4.2        | Overview                                                                                                                                    |   |

|          | 4.2               | 4.2.1         3D-CHARM: Turn Model         79                                                                                               |   |

|          |                   | 4.2.1 SD-CHARM. Turn Model                                                                                                                  |   |

|          |                   | 4.2.2 Deadlock Freedom of 5D-CHARM                                                                                                          |   |

|          |                   | 4.2.2.1 Deadlock Freedom: Inter-plane Communication                                                                                         |   |

|          |                   | 4.2.2 Deadlock Freedom: Inter-plane Communication                                                                                           |   |

|          | 4.3               |                                                                                                                                             |   |

|          | 4.0               | Results Analysis914.3.1Uniform Traffic92                                                                                                    |   |

|          |                   | 4.3.2         Hotspot Traffic         93                                                                                                    |   |

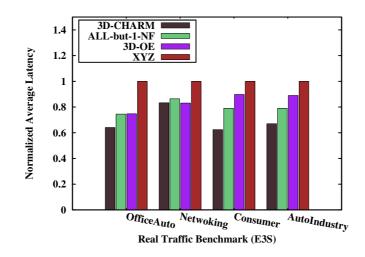

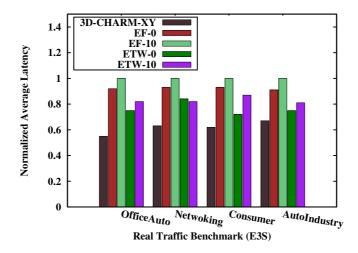

|          |                   | 4.3.3       Application Traffic       95                                                                                                    |   |

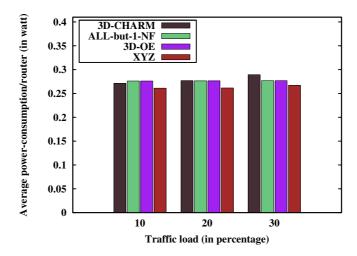

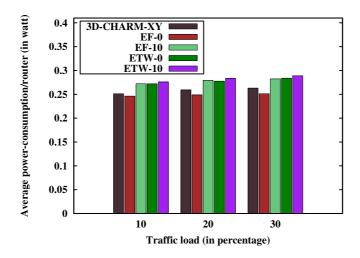

|          |                   | 4.3.4         Power Analysis         97                                                                                                     |   |

|          |                   |                                                                                                                                             |   |

|          | 4.4               | 4.3.5       Area Analysis       98         Inferences       99                                                                              |   |

|          | 1.1               |                                                                                                                                             |   |

| <b>5</b> |                   | AR: Fault-tolerant and Congestion-Aware Routing 100                                                                                         |   |

|          | 5.1               | Overview                                                                                                                                    |   |

|          | 5.2               | Proposed Method                                                                                                                             |   |

|          |                   | 5.2.1 Deadlock and Livelock Freedom of FTCAR                                                                                                |   |

|          | •                 | 5.2.2 FTCAR: Fault tolerance Analysis                                                                                                       |   |

|          | 5.3               | Results Analysis                                                                                                                            |   |

|          |                   | 5.3.1 Uniform Traffic $\ldots \ldots 107$ |   |

|   |     | 5.3.2   | Hotspot Traffic                                    | . 108 |

|---|-----|---------|----------------------------------------------------|-------|

|   |     | 5.3.3   | Application Traffic                                | . 108 |

|   |     | 5.3.4   | Power Analysis                                     | . 109 |

|   |     | 5.3.5   | Area Analysis                                      |       |

|   | 5.4 | Infere  | nces                                               | . 111 |

| 6 | Rec | onfigu  | rable Distributed Fault-Tolerant Routing Algorithm | 112   |

|   | 6.1 | Overv   | iew                                                | . 112 |

|   |     | 6.1.1   | LBDR Overview                                      | . 113 |

|   |     | 6.1.2   | Next Hop Computation Logic                         | . 115 |

|   | 6.2 | Propo   | sed Method                                         | . 115 |

|   |     | 6.2.1   | Link Failure Classification and Deadlock Freedom   | . 116 |

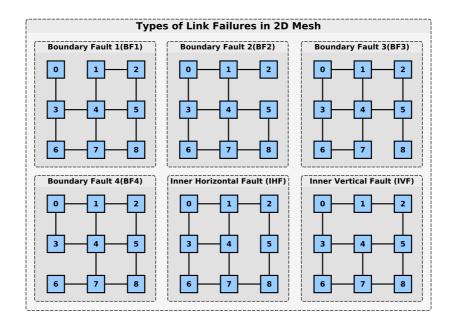

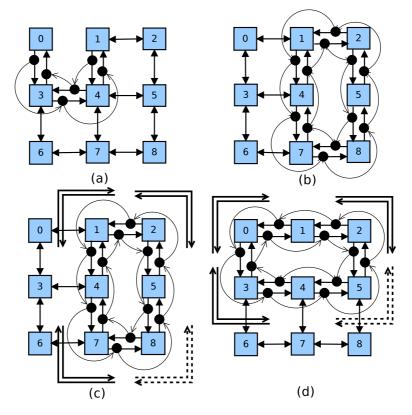

|   |     | 6.2.2   | Reconfiguration of Routing Paths                   | . 118 |

|   |     | 6.2.3   | Fault Tolerant Routing Implementation              | . 119 |

|   | 6.3 | Result  | ts Analysis                                        | . 123 |

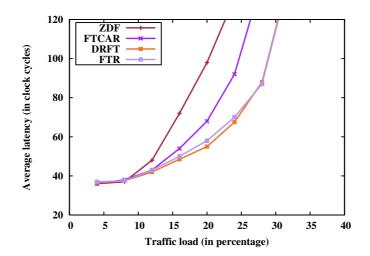

|   |     | 6.3.1   | Uniform Traffic                                    |       |

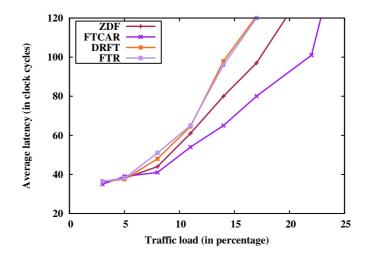

|   |     | 6.3.2   | Hotspot Traffic                                    |       |

|   |     | 6.3.3   | Application Traffic                                |       |

|   |     | 6.3.4   | Power Analysis                                     |       |

|   |     | 6.3.5   | Area Analysis                                      |       |

|   | 6.4 | Infere  | nces                                               |       |

| 7 | Con | nclusio | ns and Future Directions                           | 129   |

|   |     |         |                                                    |       |

Bibliography

134

# List of Figures

| 1.1  | Ring architecture for four routers                                                                                  | 4  |

|------|---------------------------------------------------------------------------------------------------------------------|----|

| 1.2  | Channel dependency graph for the routing function $R$                                                               | 5  |

| 2.1  | Point-to-point communication architecture                                                                           | 9  |

| 2.2  | Shared-bus communication architecture                                                                               | 10 |

| 2.3  | Segmented-bus communication architecture                                                                            | 11 |

| 2.4  | Fully-crossbar communication architecture                                                                           | 11 |

| 2.5  | Network-on-Chip (NoC) communication architecture                                                                    | 13 |

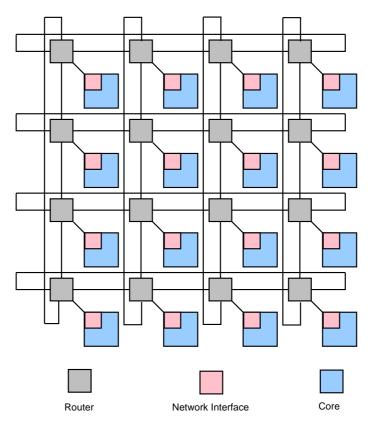

| 2.6  | 2D-Mesh topology                                                                                                    | 15 |

| 2.7  | 2D-Torus topology                                                                                                   | 16 |

| 2.8  | 3D-Hypercube topology                                                                                               | 16 |

| 2.9  | Butterfly topology                                                                                                  | 17 |

| 2.10 | Fat-tree topology                                                                                                   | 17 |

| 2.11 | Generic NoC router architecture                                                                                     | 18 |

| 2.12 | Message Composition                                                                                                 | 22 |

| 2.13 | Timing diagram for store-and-forward switching                                                                      | 23 |

| 2.14 | Timing diagram for virtual cut-through switching                                                                    | 24 |

| 2.15 | Deadlock configuration                                                                                              | 26 |

| 2.16 | An example of livelock                                                                                              | 28 |

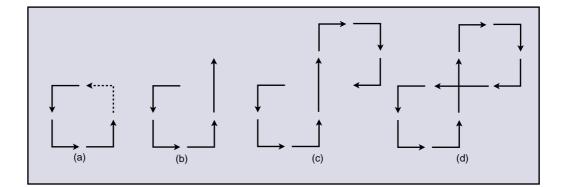

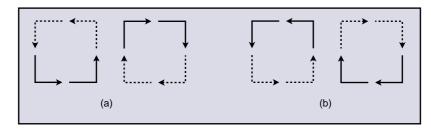

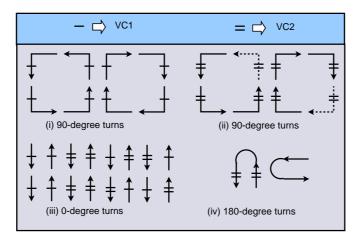

| 2.17 | Different types of turns for mesh network                                                                           | 33 |

| 2.18 | Abstract cycles for 2D mesh                                                                                         | 33 |

| 2.19 | XY turn model                                                                                                       | 34 |

| 2.20 | Six turns that form the cycle                                                                                       | 36 |

|      | Six turns that form the cycle                                                                                       | 36 |

| 2.22 | West-first turn model                                                                                               | 37 |

| 2.23 | negative-first turn model $\ldots$ | 37 |

| 2.24 | North-last turn model                                                                                               | 40 |

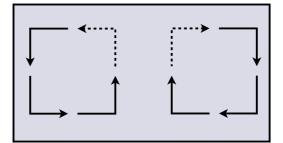

| 2.25 | Turn model for odd-even routing (a) odd columns (b) even columns                                                    | 40 |

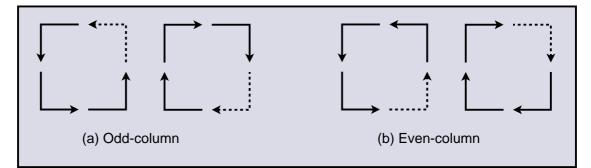

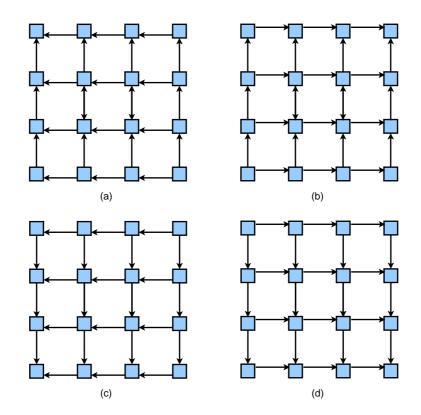

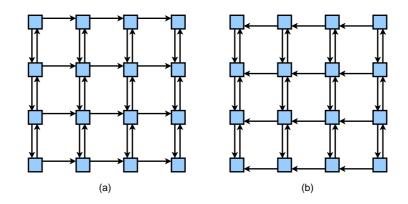

| 2.26 | Example of virtual networks for 2D mesh                                                                             | 42 |

| 2.27 | Virtual networks used by double-y routing for 2D mesh                                                               | 43 |

| 2.28 | Turn model for double-y routing                                                                                     | 43 |

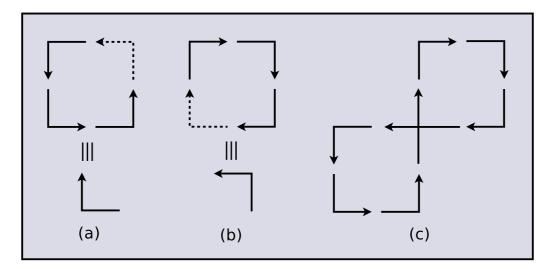

| 3.1  | Mad- $y$ turn model                                                                                                 | 50 |

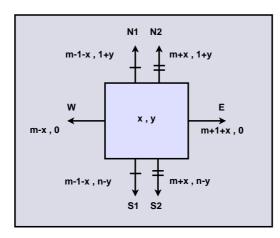

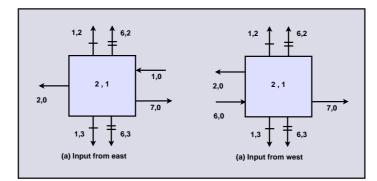

| 3.2  | Numbering for Mad- $y$ router                                                                                       | 51 |

| 3.3  | Numbering for Mad- $y$ router                                                                                       | 51 |

| 3.4  | Numbering for Mad- $y$ router                                                                                       | 52 |

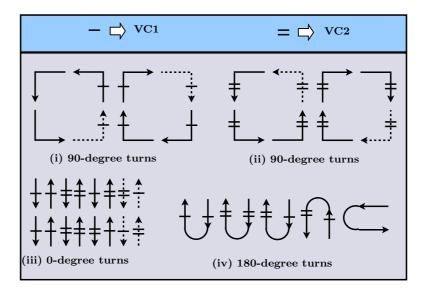

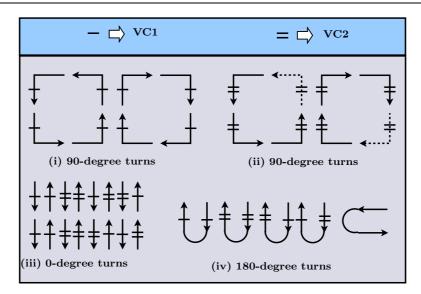

| 3.5  | LEAR turn model                                                               | 53  |

|------|-------------------------------------------------------------------------------|-----|

| 3.6  | HARAQ turn model                                                              | 53  |

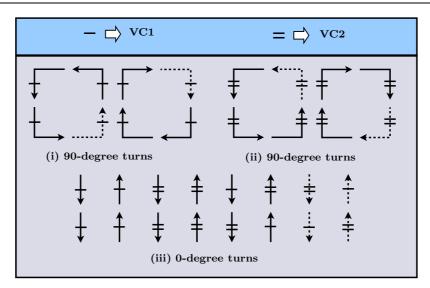

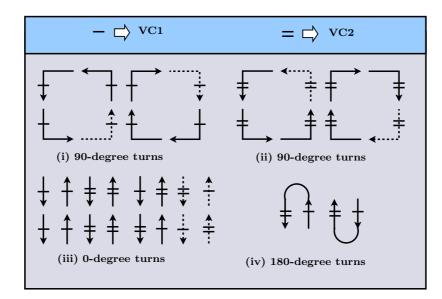

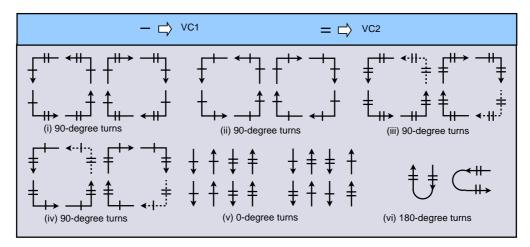

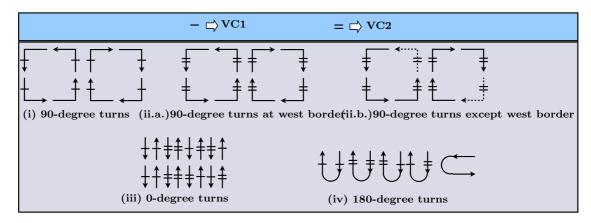

| 3.7  | 2D-CHARM turn model                                                           | 55  |

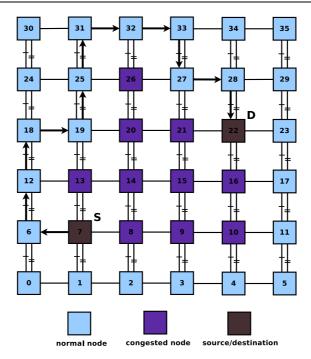

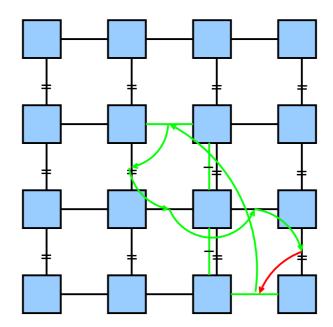

| 3.8  | Example of 2D-CHARM method                                                    | 58  |

| 3.9  | Example of indirect dependency                                                | 62  |

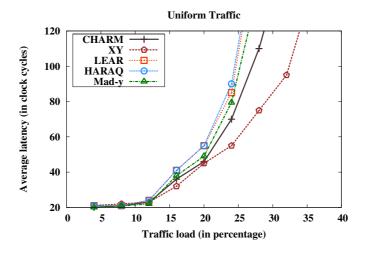

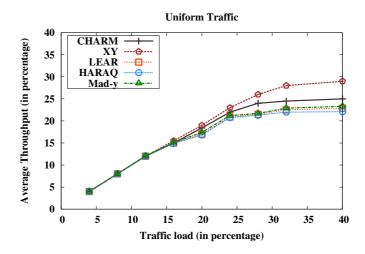

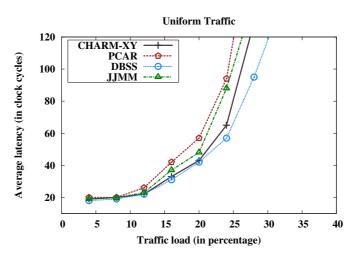

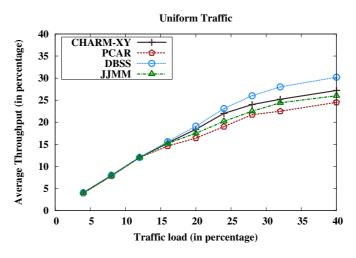

| 3.10 | Average latency under uniform traffic for double-y network                    | 67  |

| 3.11 | Average throughput under uniform traffic for double-y network                 | 67  |

| 3.12 | Average latency under uniform traffic for double-xy network                   | 68  |

| 3.13 | Average throughput under uniform traffic for double-xy network                | 68  |

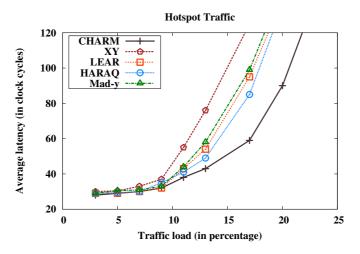

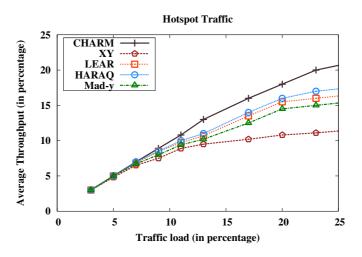

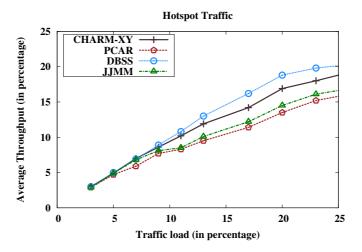

| 3.14 | Average latency under hotspot traffic for double-y network                    | 70  |

| 3.15 | Average throughput under hotspot traffic for double-y network                 | 70  |

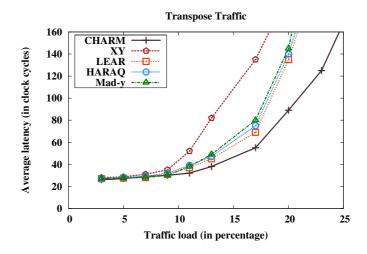

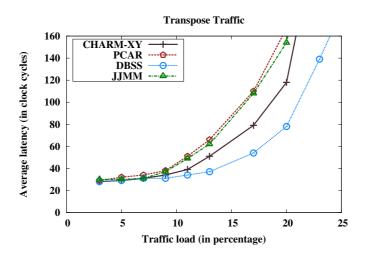

| 3.16 | Average latency under transpose traffic for double-y network                  | 71  |

|      | Average throughput under transpose traffic for double-y network               | 71  |

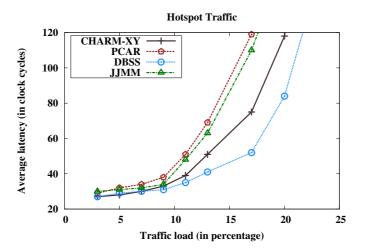

| 3.18 | Average latency under hotspot traffic for double-xy network                   | 72  |

|      | Average throughput under hotspot traffic for double-xy network                | 72  |

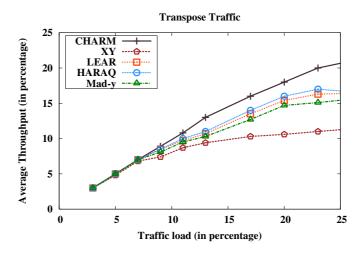

|      | Average latency under transpose traffic for double-xy network                 | 73  |

|      | Average throughput under transpose traffic for double-xy network .            | 73  |

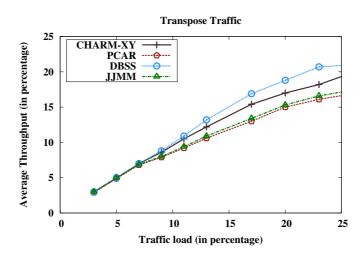

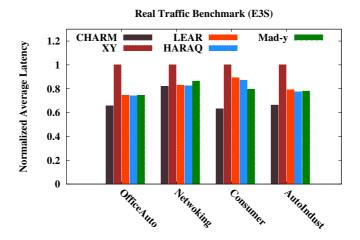

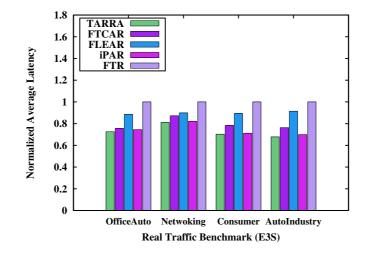

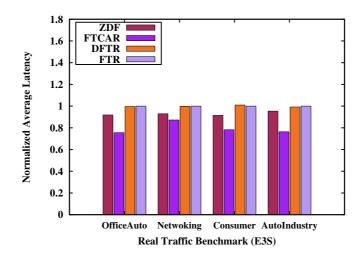

|      | Performance for application traces for double-y network                       | 74  |

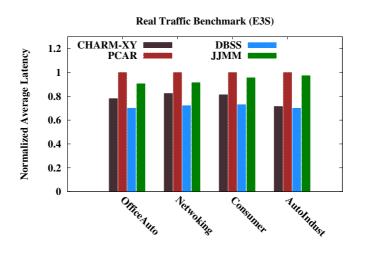

|      | Performance for application traces for double-xy network                      | 74  |

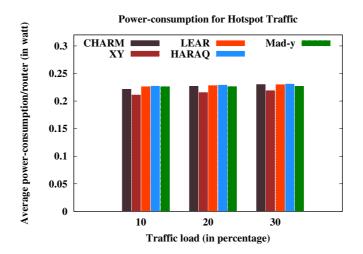

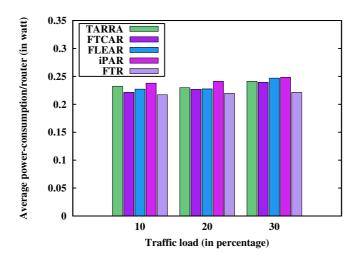

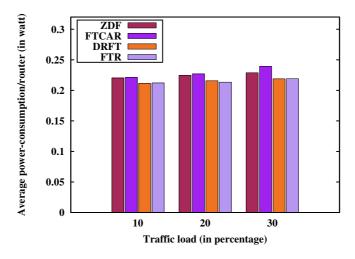

|      |                                                                               | 75  |

|      | Power consumption results under hotspot traffic for double-xy network         | 75  |

|      |                                                                               |     |

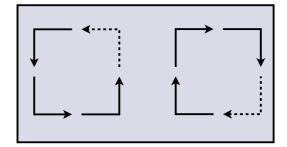

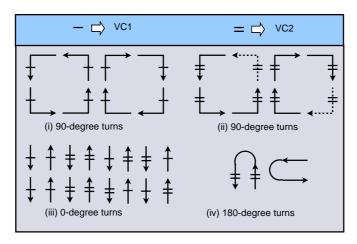

| 4.1  | Turn model for $YZ$ -plane of 3D-CHARM                                        | 80  |

| 4.2  | Turn model for XY-plane of 3D-CHARM                                           | 80  |

| 4.3  | Turn model for $XZ$ -plane of 3D-CHARM                                        | 80  |

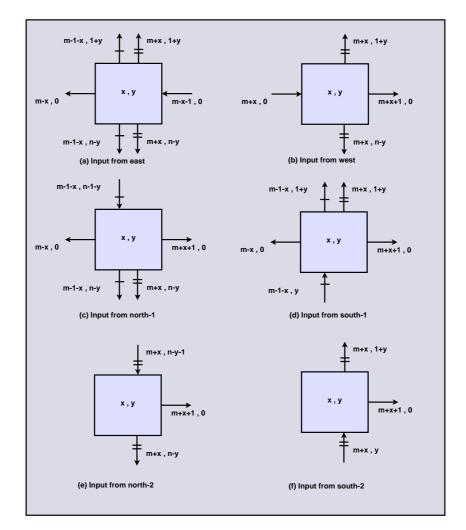

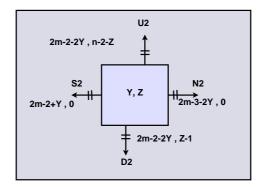

| 4.4  | Numbering for router of $R_1$ routing algorithm $\ldots \ldots \ldots \ldots$ | 87  |

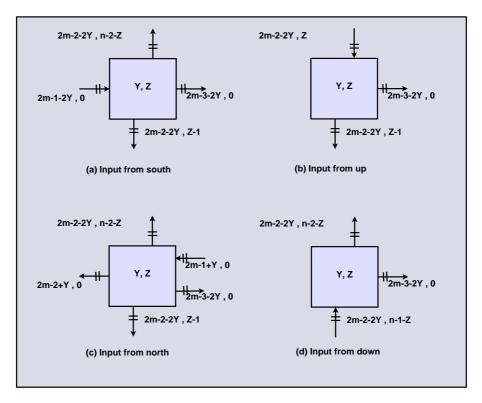

| 4.5  | Numbering for router of $R_1$ routing algorithm for the each input            |     |

|      | channel                                                                       | 88  |

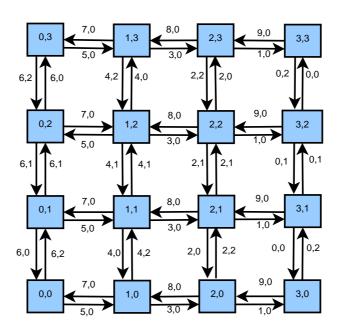

| 4.6  | Each router $(Y, Z)$ in $4 \times 4 YZ$ -plane for $R_1$ routing function     | 88  |

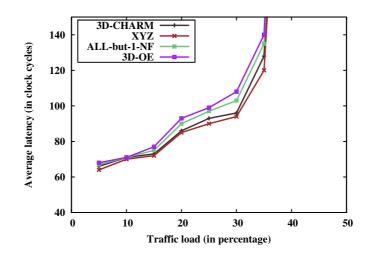

| 4.7  |                                                                               | 93  |

| 4.8  | 0                                                                             | 94  |

| 4.9  | Average latency under hotspot traffic for $4 \times 4 \times 4$               | 94  |

|      |                                                                               | 95  |

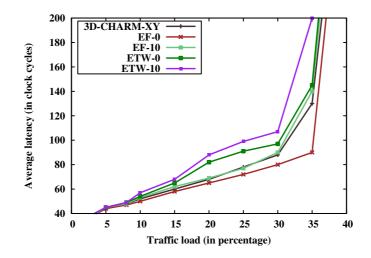

|      |                                                                               | 96  |

|      | 1 1                                                                           | 96  |

|      |                                                                               | 97  |

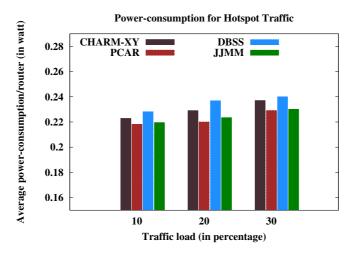

| 4.14 | Power consumption results under hotspot traffic for $4 \times 4 \times 3$     | 98  |

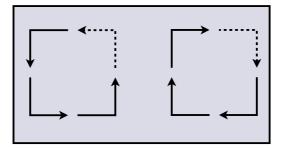

| 5.1  | FTCAR turn model                                                              | 102 |

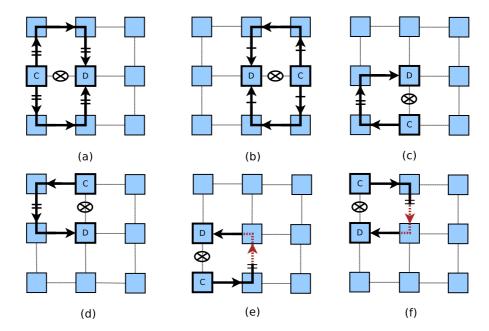

| 5.2  | Tolerating single link failures for different packet directions 1             |     |

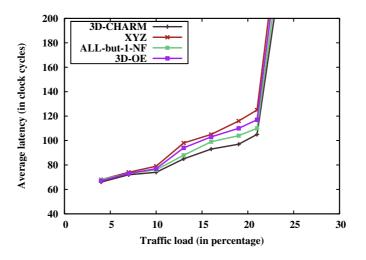

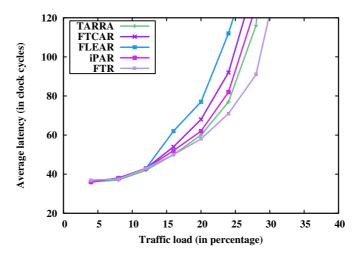

| 5.2  | Average latency under uniform traffic                                         |     |

| 5.3  | Average latency under hotspot traffic                                         |     |

| 5.5  | Performance for application traffic                                           |     |

| 5.6  | Power consumption under hotspot traffic                                       |     |

| 0.0  |                                                                               | 10  |

| 6.1 | Routing restrictions for $xy$ Routing for $3 \times 3$ Mesh |

|-----|-------------------------------------------------------------|

| 6.2 | LBDR Router                                                 |

| 6.3 | Types of link failure in the 2D mesh                        |

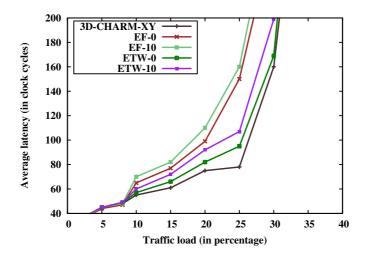

| 6.4 | Channel dependency graphs for different mesh boundaries 117 |

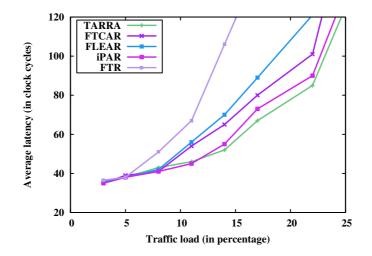

| 6.5 | Average latency under uniform traffic                       |

| 6.6 | Average latency under hotspot traffic                       |

| 6.7 | Performance for application traffic                         |

| 6.8 | Power consumption under hotspot traffic                     |

# List of Tables

| 3.1 | Prohibited routing turns for different routing algorithms                    | 56  |

|-----|------------------------------------------------------------------------------|-----|

| 3.2 | Route computation function for 2D-CHARM                                      | 59  |

| 3.3 | Route computation function for routing subfunction $R_1$                     | 61  |

| 3.4 | Route computation function for the routing function $R_2$                    | 64  |

| 3.5 | Route computation function for the new routing function $R_3$                | 65  |

| 3.6 | Area Requirement                                                             | 76  |

| 3.7 | Area Requirement                                                             | 76  |

| 4.1 | Route computation function for XY-plane of 3D-CHARM                          | 83  |

| 4.2 | Route computation function for $XZ$ -plane of 3D-CHARM                       | 84  |

| 4.3 | Route computation function for $YZ$ -plane of 3D-CHARM                       | 85  |

| 4.4 | Route computation function for the $R_1$ of $YZ$ -plane of 3D-CHARM          | 86  |

| 4.5 | Area Requirement                                                             | 98  |

| 5.1 | Area Requirement                                                             | 111 |

| 6.1 | Routing and connectivity bits of $xy$ routing for $3 \times 3$ mesh $\ldots$ | 115 |

| 6.2 | Reconfigured paths for IHF boundary                                          | 120 |

| 6.3 | Reconfigured paths for IVF boundary                                          | 121 |

| 6.4 | Area Requirement                                                             | 127 |

## Chapter 1

# Introduction

The current Chip Multiprocessors (CMPs) and Multi-Processor Systems-on-Chip (MPSoCs) architectures have replaced the single core systems due to their scalability issues. Intel Lab has developed terascale processor [98], a single chip cloud computer consists of 48 cores on same silicon CPU chip. This development is intended of achieving the scalable communication, power consumption and on-chip performance for the near future. Other industrial examples include Tilera's *TILE*-Gx72 and *TILE*64<sup>TM</sup> [4] processors. These examples show the increasing growth of integrating multiple components on a single silicon chip, and this will continue till near future. As the number of cores is increasing, communication among them is becoming challenging for these multi-core architectures. This growth leads to the paradigm shift from computation-centric designs to communication-centric designs.

In the beginning, the integrated chips had deployed a small number of processing elements and interconnected them using the conventional interconnects such as ring [26], cross-bar, shared-buses and point-to-point (P2P). In P2P techniques, a pair of processing elements is interconnected via dedicated link (wire). Thus, because of this dedicated link, the P2P interconnects based systems are able to offer 100% communication bandwidth. However, as the number of cores are increasing, it results in increased wire density, thus, for multi-core architectures, these are not suitable candidates. The shared-bus architectures are simple as far as the number of processing elements is less. With an increase in the number of such elements, the arbitration delay is also increasing and results into the bandwidth bottleneck. Crossbar designs interconnect a set of cores to another set of cores in a matrix fashion. However, the power and area constraints prevent their use in multicore systems. The ring-based communication systems interconnect the processing elements in a close loop (ring topology). In ring architecture, the communication becomes slow because the messages must cross other components of the network between source and the destination. Moreover, if one of the elements gets down, it affects the whole network. In short, the increasing complexity, bandwidth bottleneck and communication delay are the main limiting factors of traditional communication architecture based System-on-Chip (SoC). To address these communication issues for multi-core architectures, Network-on-Chip (NoC) has been introduced as a viable and scalable substitute to traditional bus-based architectures for intercore communication.

The overall performance of NoC depends on several network parameters such as topology, switching technique, flow control, and routing strategies. This thesis is focused on routing algorithms. A routing algorithm affects several nonfunctional requirements of an NoC-based system. Performance, reliability, energy consumption, power dissipation, thermal aspects, and fault tolerance are among the major parameters that are affected by the routing algorithm. Significant research has been published on the improvement of routing algorithms for the parallel and distributed computing domains. The main issues addressed include the development of high-performance, fault-tolerant and low cost (power and area) router microarchitectures, the development of bandwidth-aware and contention-aware selection policies, and the design of deadlock-free highly adaptive routing functions. In all cases, routing function (one phase of routing algorithm) has a significant effect on the overall performance of any routing algorithm [46].

### 1.1 Routing Overview

A routing algorithm computes the path from source node to the destination node. The routing algorithm can be either deterministic or adaptive. The deterministic routing scheme always provides the same path between source and the destination nodes irrespective of network congestion status. However, an adaptive scheme uses current network status in making the routing decision and may compute different output channel for different packets. The deadlock is a major issue in designing any adaptive routing algorithm. A deadlock occurs when a set of packets cannot advance toward their destination because the buffers requested by them are full [26]. The blocked packets form a deadlock configuration. Packets, involved in deadlock configuration, are waiting for each other in a cyclic manner to release the resources (buffer), thus blocked forever.

The deadlocks are severe to any routing algorithm as they can disrupt the communication by paralysing network operations. To avoid deadlocks, NoC designers use either deadlock avoidance or deadlock recovery. In deadlock avoidance methods, it is ensured that a deadlock never occur. On the contrary, deadlock recovery method detect deadlock in the network, then recover from it. The deadlock avoidance methods are generally preferred over deadlock recovery methods because recovery methods impose an overhead of deadlock detection and then buffer releasing that may degrade the network performance considerably.

To avoid deadlocks, researchers have used two main theories; Dally's theory [17] and Duato's theory [24]. The first theory does not allow cyclic dependencies among channels. Whereas, the other one allows cyclic dependencies provided that there exists deadlock free routing subfunction. The details of routing algorithms and deadlocks are discussed in Sections 2.5 and 2.6.

#### 1.2 Motivations

With deterministic routing, packets can be routed over single output channel at each node. Thus, it is mandatory to remove all cyclic dependencies between network channels in order to achieve deadlock freedom. In adaptive routing, packets often have several options for routing at each node. Thus, it is not mandatory to eliminate all cyclic dependencies between channels, provided that each packet can be forwarded on a route whose channels are not involved in the cyclic dependencies. The channels involved in these acyclic routes are considered as *escape channels* from deadlocks (cycles). Based on the extensive literature survey on challenges in routing algorithm, following are the motivations of this thesis:

1. The first motivation for the proposed routing algorithms is derived from the fact that a less restrictive routing algorithm offers a high degree of adaptiveness [46]. Most of routing algorithms proposed in the recent literature [70, 36, 68, 71, 45, 34, 32, 33] achieve deadlock-freedom by forcibly restricting certain routing turns so that the CDG remains acyclic. This acyclic CDG requirement for the deadlock-freedom makes these algorithms more restrictive, thus reduces the degree of adaptiveness. If we relax this requirement for these algorithms, we can be blessed with a less restrictive routing algorithm. The main focus of this proposed work is to relax this requirement by allowing cycles in the CDG provided that ECDG is acyclic (using Duato's theorem [24]). We have explained our point by comparing with two recent algorithms LEAR [34] and HARA [32]. It should be noted that LEAR and HARA routing algorithms are based on Mad-y [45] turn model.

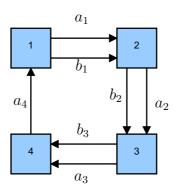

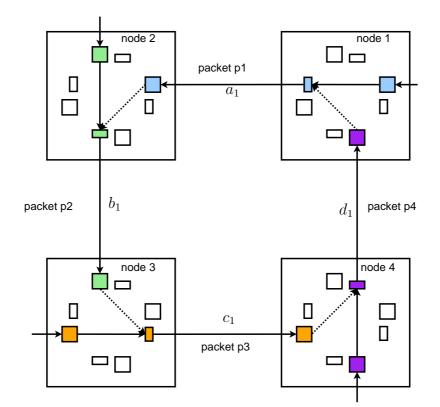

We present an example which shows that a routing scheme would be deadlockfree, even if there exist cyclic dependencies between channels. Figure 1.1 shows a ring consisting of four routers (1, 2, 3 and 4). Each router is connected to the adjacent router using two channels  $a_i$  and  $b_i$ ,  $i = \{1, 2, 3\}$ (physical or virtual) except the routers 4 and 1. Router 4 is connected to router 1 using a single channel  $a_4$ .

Figure 1.1: Ring architecture for four routers

The routing function R for the ring is defined as below

$$R = \begin{cases} a_i & , \forall j \neq i \\ b_i & , \forall j > i \end{cases}$$

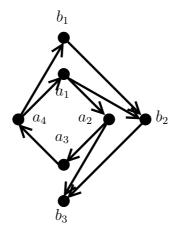

Figure 1.2 shows the channel dependency graph for the routing function R. The dependencies are because of followings:

- (a) If a packet is at the router 1 and the destination is router 3, it can occupy channel  $a_1$  and request channels  $a_2$  and  $b_2$ .

- (b) If a packet is at the router 2 and the destination is router 4, it can occupy channel  $a_2$  and request channels  $a_3$  and  $b_3$ .

Figure 1.2: Channel dependency graph for the routing function R

- (c) If a packet is at the router 3 and the destination is router 1, it can occupy channel  $a_3$  and request channel  $a_4$ .

- (d) If a packet is at the router 4 and the destination is router 2, it can occupy channel  $a_4$  and request channels  $a_1$  and  $b_1$ .

We can observe that there exist cyclic dependencies among  $a_i$  channels. However, it is clear from Figure 1.2 that the  $b_i$  channels are not involved in any cyclic dependencies. Thus, they are always free (empty). We prove the deadlock-freedom of R by contradiction. We assume that there is a deadlock in routing function R. There must exist a deadlock configuration, and any deadlock configuration can involve only  $a_i$  channels as the  $b_i$  channels are always empty. Although, Figure 1.2 depicts that the  $a_i$  channels involved in the cyclic dependencies, but this deadlock configuration will not be legal. At router 1, channel  $a_1$  can be occupied by a packet that is destined for either router 2 or 3 or 4. At router 2, this packet can use  $b_2$  and  $b_3$ (always empty channels) channels for these destinations thus breaking the cyclic dependency. We have proved that the routing function R with cyclic dependencies does not have any deadlock-configuration. Thus, it would be deadlock-free.

2. In on-chip communications, reliability is a critical factor in multi-core systems. It is affected by transient and/or permanent faults. Faults affect the functionality and can degrade the performance of on-chip networks. Thus, it has become essential to design on-chip networks that can tolerate faults. The second motivation for this thesis to achieve fault-tolerance to make communication more reliable.

### 1.3 Objectives

The objectives of this thesis are as stated below:

- 1. To design a turn model to provide high degree of adaptiveness for the 2D mesh network. The ultimate aim is to add more functionality (routing turns) to virtual channels of existing algorithms minimally or non-minimally around hotspot and congested areas of the network to achieve the high degree of adaptiveness.

- 2. To extend the 2D turn model for three-dimensional mesh to improve the network performance.

- 3. To implement reconfigurable and fault tolerant routing algorithms by analyzing deadlock-freedom to bypass faulty links of the network.

#### **1.4** Contributions of the Thesis

The major contributions of this thesis are as follows:

- 1. We propose a novel turn model that provides high degree of adaptiveness for a 2D mesh. The end result is that the proposed turn model reduces the number of restrictions on routing turns and hence is able to provide path diversity through additional minimal and non-minimal routes between the source and destination. Based on turn model, we have presented a highly adaptive and congestion-aware routing method (CHARM). The proposed method is implemented using double-y network.

- We have extended aforementioned 2D turn model for three dimensions (3D) to high achieve adaptivity. It uses one, two and two virtual channels in X, Y and Z dimensions, respectively.

- 3. We have developed a highly adaptive and fault-tolerant routing algorithm for 2D mesh topology. The proposed algorithm is able to handle single link faults within a 2D mesh. It can also handle multiple link faults if fault's boundary do not overlap with each other.

4. In an MPSoC or CMP architecture, the reliability of NoC is affected by transient and/or permanent faults. Faults affect the functionality and can degrade the performance of on-chip networks. We have designed a fault-tolerant and reconfigurable routing algorithm for the 2D mesh topology. The presented approach can handle single link faults within the 2D mesh, and it uses Logic Based Distributed Routing (LBDR) as its implementation.

In this thesis, we mainly focus on the development of highly adaptive and faulttolerant routing algorithms for mesh networks with wormhole flow control. Our proposal tries to identify non-essential restrictions and remove these to improve adaptivity of underlying architecture in terms of routing function. The effectiveness of proposed algorithms is shown by evaluating them for both real and synthetic traffic profiles. In addition, power and area overheads are also analyzed.

### 1.5 Thesis Outline

The remainder of the thesis is partitioned into three categories i.e. the introductory chapter, contributory chapters and the concluding chapter. The introductory chapter (Chapter 2) demonstrates the background required for understanding the concepts of on-chip networks. The contributory chapters include four chapters, each presenting the proposed work. Chapter 3 presents the highly adaptive and congestion-aware routing method for the 2D mesh. A three dimensional extension to proposed 2D turn model is presented in Chapter 4. It also presents the analysis how this two-dimensional method can be applied to three dimensions. Chapter 5 provides the fault tolerance analysis of the 2D turn model. It also introduces fault tolerant routing technique for a 2D mesh. Chapter 6 provided another fault tolerant and reconfigurable routing method using LBDR. It can handle all single link failures. Finally, Chapter 7 concludes the research work proposed in this thesis and provides future directions.

## Chapter 2

# Networks-on-Chip (NoCs)

The device scaling has resulted in an exponential increase in the circuit performance that sustained the recent microelectronic evolution. The 28nm silicon technology is already in use for the production. A single chip with 32nm technology consists of billions of transistors with a descent chip density of 1.5  $Mgate/mm^2$ . Decreasing returns and the increased design complexity (chip density, etc.) of a single processor system have resulted in the emergence of many-core architectures in the form of multi-core Systems-on-Chip (SoCs).

An SoC is a complex computing system which consists of processing elements, data converters, hardware accelerators, peripheral interfaces, I/Os, on-chip memory, and other components. For a specific application domain, it represents a complex device that provides all the needed hardware and electronic circuits to form a working system. An SoC is generally customized for a specific application which is very similar to the traditional application-specific integrated circuit (ASIC). However, the main emphasis is not on specialized hardware design for the SoCs, like conventional ASICs. SoCs utilize reusable existing components as much as possible so that these can reduce the production of newly designed elements of the chip. These reusable components known as intellectual-property (IP) cores and include both the soft and hard core components.

In the current Silicon-technology era, the main development perspective is shifted towards increasing the number of cores in multi-core systems from increasing the operating frequency of a single core processor. As the number of cores is increasing, the communication among the cores is becoming more challenging for these multi-core architectures. These trends have resulted in a paradigm shift towards communication-centric designs from computation-centric designs.

# 2.1 Why NoC: Evolution of On-chip Communication Architectures

A communication infrastructure is required to interconnect various application specific integrated circuits (ASICs), memories, processors and other elements on a single-chip. The basic requirements for a good communication infrastructure include high performance, low power, and low latency. Thus, the efficient implementation of SoCs requires scalable and bandwidth-aware communication infrastructure. The two major technological challenges in the design of an efficient communication architecture for SoCs are (i) reducing the huge computing power (ii) handling the large amount of traffic generated by number of concurrently running applications.

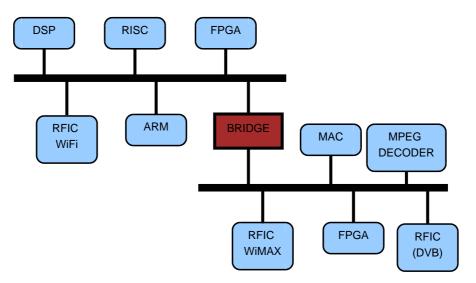

Traditionally, SoCs employ communication schemes [26], namely point-to-point, rings, crossbars, and buses. By connecting a pair of elements with a dedicated link, the point-to-point architectures (Figure 2.1) provide the advantage of 100% bandwidth availability. However, these schemes are not well scalable in terms of cost, design efforts, complexity, and flexibility. As the number of cores increases, these also result in the increased wire density, thus not suitable for the many-core SoCs.

Figure 2.1: Point-to-point communication architecture

In order to eliminate dedicated link requirement of the point-to-point architectures, the bus-based architectures (Figure 2.2) can be used. These architectures interconnect a small number (few tens) of cores in a cost-effective manner and result into reduced overall design complexity. The main advantage of bus-based

Figure 2.2: Shared-bus communication architecture

architectures is their simplified interconnection design. However, due to sharing property, these architectures limit the maximum achievable bandwidth. In addition, electrical noise, variability, and crosstalk are growly serious issues with recent technology. The use of long global wires makes the shared bus systems more vulnerable to these problems. Moreover, the addition of new components can deteriorate performance of buses drastically. Because, with miniaturization, the propagation delay of long global wires is monotonously increasing and thus, with new chip generations, the clock frequency of the bus system is reducing.

The segmented (hierarchical) bus structure provides a solution to the bandwidth constraints of the shared bus interconnect. As shown in Figure 2.3, it interconnects a bus structure with another bus structure using a bridge component. The computation of optimum settings for the segmented bus is very time-consuming and complex [14]. Because, the bus arbitration of segmented bus is distributed in nature which combines the operations of all arbitration units.

Crossbar designs interconnect a set of cores to another set of cores in a matrix fashion. However, the power and area constraints prevent their use in multicore systems. The ring-based communication systems interconnect the processing elements in a close loop (ring topology). In ring architecture, the communication becomes slow because the messages must cross other components of the network between the source and the destination. Moreover, if one of the elements gets down, it affects the whole network. In short, the increasing complexity, bandwidth bottleneck and communication delay are the main limiting factors of traditional

Figure 2.3: Segmented-bus communication architecture

communication architecture based System-on-Chip (SoC). To address these communication issues for multi-core architectures, Network-on-Chip (NoC) paradigm is introduced as a viable and scalable substitute to traditional bus-based architectures for intercore communication.

Figure 2.4: Fully-crossbar communication architecture

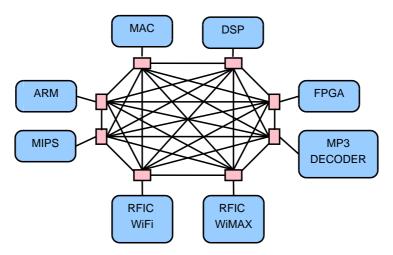

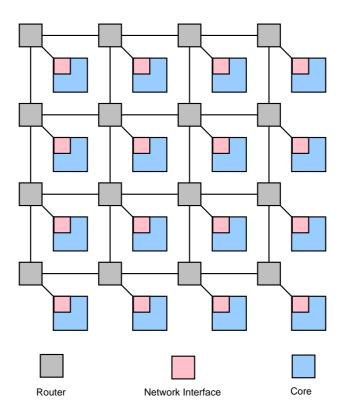

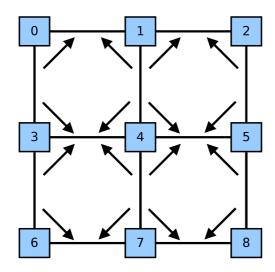

Figure 2.5 shows  $3 \times 3$  mesh on-chip network. The main idea behind the development of NoC as a communication paradigm is to route the packets instead of the wires [19]. To route a message/packet generated by one core to another, the NoC uses several routers or switches.

The main purpose of designing SoC is to develop applications which are generally specific to embedded system domain. We can classify the SoCs architectures on the basis of the use of NoC into two major categories; Chip Multiprocessors (CMPs)

and MultiProcessors System-on-Chip (MPSoCs). If the multi-core SoC consists of heterogeneous core elements, the SoC is known as MPSoC. If the cores of SoCs are of homogeneous in nature, the SoC is known as CMP. The cores communicate with each other by sending and receiving packet to/from other cores. This interaction is generally of parallel nature in the embedded applications. The major designing factors of these multi-processor architectures include low communication latency and low power. In portable electronic appliances and electronic-handhelds, the power is completely dependent on the battery life. Thus, the main issue to design the NoC-based CMPs/MPSoCs architectures is the power constraint that depends on the chip area.

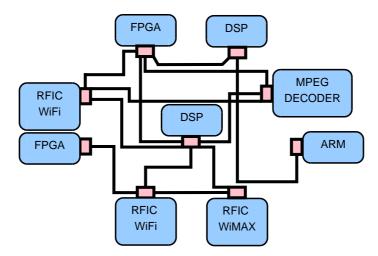

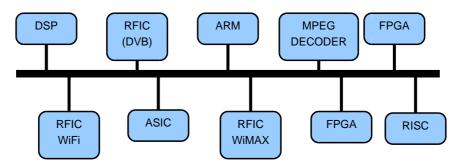

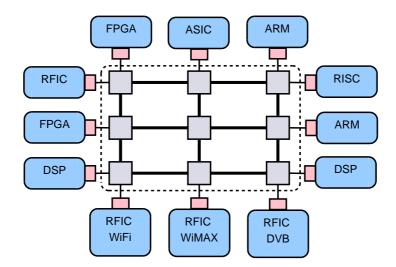

In CMP architectures, a tile includes three components; IP-core, a router and a network interface. The IP-core consists of an IO interface, a memory controller (MCtrl), a global (shared) memory, a local memory block, some CPU blocks and some other elements. Each router is connected to the IP-core using a network interface. The purpose of the network interface is to decompose a data packet into a number of flits when one core sends the data to another. The network interface is also responsible for the assembling the flits to reconstruct the data packet at the receiving tile. Similarly, an MPSoC architecture can have different types of IP-cores such as FPGA-based configurable block, an ASIC component, a bus-based microprocessor system (such as RISC, MIPS, ARM or processor system), a digital signal processor (DSP), a shared memory, or any other type of IP-core.

The NoC architecture has already been used as the communication backbone for current embedded SoC applications. The Xbox-360 [2] and Cell Broadband Engine Processor [64] gaming consoles are examples of potential commercial products of multiprocessor applications which rely on NoC as communication architecture. The Xbox-360 gaming console is an example of CMP architecture comprised of graphics processing unit (GPU), memory, I/O units and CPU units. The units are connected using node crossbar/queuing as the number of elements are small. The node crossbar/queuing is similar to the single crossbar-switch of a NoC router. Cell Broadband Engine Processor (also known as Cell Processor) is a result of joint efforts of Toshiba, Sony, and IBM. It incorporates a 64-bit power processor element (PPE), eight specialized processors called synergistic processor elements (SPEs), a high-bandwidth bus interface, and a high-speed memory controller. All units are interconnected through four slotted rings and integrated on chip. The Cell Processor is dedicatedly designed for Playstation 3 Game Console. The on-chip network

Figure 2.5: Network-on-Chip (NoC) communication architecture

paradigm is also accepted by the industry as the communication infrastructure for complex Systems-on-Chip (SoC) to replace shared buses and dedicated wires. Intel's terascale processor [98] and Tilera's TILE-Gx72,  $TILE64^{TM}$  [4] processors are the few commercial examples who have adopted mesh based NoC.

Implementation of an NoC includes several designing characteristics such as network topology, flow-control methods, routing methods, quality-of-service and switching methods. This chapter describes the basics and general theory [26, 85, 20] about these characteristics of interconnection networks.

### 2.2 NoC Topologies

The network topology defines how the different IP-cores of an MPSoC/CMP are interconnected to each other through routers and network interfaces. As the selection of specific flow-control method and routing algorithm depends largely on the network topology, the very first step in designing on-chip network is the selection of the topology. The network topology not only defines the static arrangement of network components (routers, channels, and NIs), it also specifies other details such as the bit-rate and bandwidth of each channel, the number of stages, bisection bandwidth, path diversity, and the radix of the router.

The network designers select a specific topology on the basis of its performance and the implementation complexity-cost. The network performance is defined by the communication bandwidth, power utilization and network throughput. The implementation complexity-cost has three main components; (a) length and density of wires (b) router degree (number of channels at each router) (c) number of metal layers needed to realize the network.

A network node may act as either router node or terminal node or both. A router node routes packets from input ports to output ports. A terminal node acts as a source and sink for the packets. On the basis of the role of the node in the network, a topology can be classified into two categories direct and indirect. In a direct topology, every network node acts as both a router and a terminal. On the other hand, in an indirect topology, a network node acts as either a router or a terminal. In a direct network, packets are routed directly from one terminal node to other. With an indirect network, packets are routed through a sequence of intermediate router nodes between the source and the destination. Till now, the majority of the NoC designs have utilized direct networks. The main advantage of a direct network is that a router node is co-located with the terminal node so that each router can use various resources of a terminal node. Moreover, it is more suitable to place routers with the terminal nodes in area-constrained systems like NoCs.

#### 2.2.1 Direct Topologies

A variety of network topologies has been modeled and designed using their graphtheoretical characteristics for on-chip networks. The majority of the implemented topologies are orthogonal topologies. In an orthogonal topology, all of its vertices (nodes) are organized in an n-dimensional orthogonal space, and every edge (channel) is organized in such a way that it produces a displacement in a single dimension. Thus, we can number the network nodes using their coordinates in the n-dimensional space. The advantage of using orthogonal topologies is that the hardware implementation of a routing algorithm becomes efficient.

Figures 2.6, 2.7 and 2.8 show the most commonly used orthogonal direct topologies; 2D-dimensional mesh (k-ary n-mesh), 2D-torus (k-ary n-cube) and 3D-hypercube. Mesh topology (Figures 2.6) is among the most popular and important NoC topology for large-scale MPSoCs and CMPs architectures. The main advantages of mesh topologies are their good scalability, regularity, and simplicity. Most of the industrial and academic MPSoCs and CMPs use mesh-based NoC topologies as their communication backbone.

Figure 2.6: 2D-Mesh topology

Formally, an n-dimensional mesh has  $k_0 \times k_1 \times \ldots \times k_{n-2} \times k_{n-1}$ ,  $k_i$  nodes along each dimension *i*, where  $k_i \ge 2$  and  $0 \le i \le n-1$ . Every node *X* is represented by *n* coordinates,  $(x_{n-1}, x_{n-2}, \ldots, x_1, x_0)$ , where  $0 \le x_i \le k_i - 1$  for  $0 \le i \le n-1$ .

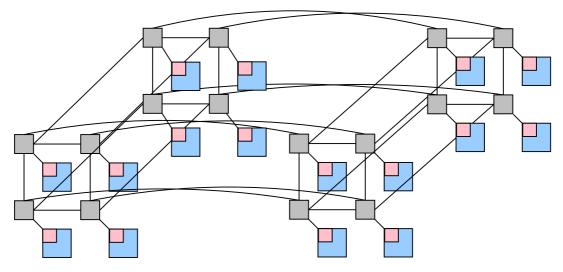

In torus topology, as shown in Figure 2.7, each node has the same degree. The mesh topology has the disadvantage of increased long hop count between opposite borders. The torus topology eliminates this disadvantage. In this topology, the routers at the border are directly connected to the routers at the opposite border. Thus, it reduces the hop count on a path. Because of edge symmetric property, the torus is able to distribute traffic more evenly across the network. The hypercube (Figure 2.8) is another commonly used topology for 3D NoCs. It is considered as a special case of mesh topologies.

#### 2.2.2 Indirect Topologies

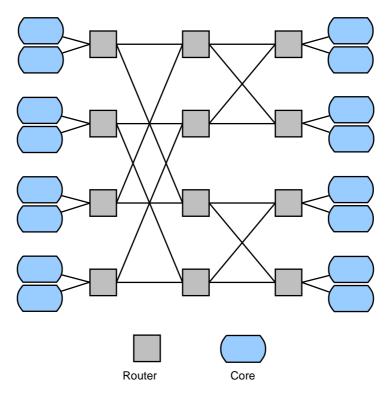

Figure 2.9 shows an example of 2-ary 3-fly butterfly topology. The butterfly topology is a clear example of the difference between router node and the terminal node. The router nodes are in the middle (shown by rectangles) and terminal nodes are

Figure 2.7: 2D-Torus topology

Figure 2.8: 3D-Hypercube topology

on the borders. The router node accepts packets at its input port and computes their destinations using underlying routing algorithm, then routes packets to the output channel.

Figure 2.9: Butterfly topology

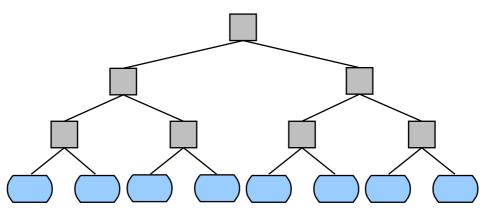

Figure 2.10 shows an example of fat tree topology that logically represent a binary tree. In a fat tree, packets are forwarded towards the root till they reach a common ancestor and then forwarded down towards the destination. Each router in the fat tree has a logical degree of four. Though, the links in higher-level nodes are much wider than those in the lower levels.

Figure 2.10: Fat-tree topology

### 2.3 NoC Router: Generic Architecture

A major challenge towards the multi-core architecture is the designing an efficient router microarchitecture. The performance factors for a NoC router includes latency with area and power constraints. A router is capable of receiving packets at the input ports, computes the output port depending upon the destination address using the routing algorithm, and then routes the packet along the appropriate output channel. For a specific on-chip network, the router microarchitecture is generally unique. It depends on various network characteristic such as quality of service, chosen routing method, switching mechanism implementation, flowcontrol methods, and quality of service.

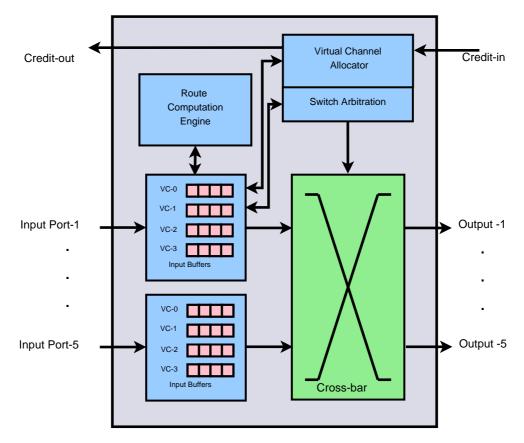

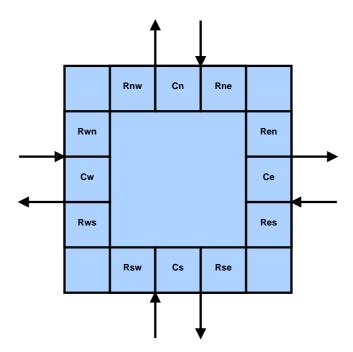

Figure 2.11 shows a generic router microarchitecture for a 2D mesh topology. It is composed of five input-output (I/O) ports, one for each of the directions (North, South, East, West, and Local). The Local I/O port is connected to the corresponding IP-core through a network interface. Typically, an NoC router has five major components as following:

Figure 2.11: Generic NoC router architecture

- 1. Buffer: The First-In First-Out (FIFO) buffers are used to hold the transiting packet. Each input and/or output physical channel is associated with one buffer. The transit packet can be incoming and outgoing packet in a router. Depending upon the requirement, different NoC routers implement FIFO buffers either at input ports or at output ports or at both places. This implementation reduces the data buffering cost. If a packet (say p1) occupies a buffer for a channel, the other packet (say p2) cannot access the physical channel, even if p1 is blocked. In an alternative appraoch, the buffer can be multiplexed into the number of virtual channels in order to provide quality of service and deadlock-freedom. These logical channels are multiplexed across the physical channel as shown in the Figure 2.11. As the buffer adds significant cost (power and area) to a router, some recent router implementations [100, 42] have eliminated the need of virtual channels.

- 2. Route Computation Engine: The task of Route Computation Engine is to compute the appropriate output channel for an incoming packet. This unit implements the routing scheme. Typically, NoC routers make use of two different implementations of the route computation engines: table based routing and routing finite state machine. The details of routing algorithms and their implementations are discussed later in Section 2.5.3

- 3. Arbiter: Multiple packets can request same output channel simultaneously. The purpose of arbitration unit is to resolve these concurrent requests for the same output channel. It provides the arbitration among them. When a packet requests a particular output channel and if that channel is occupied by the other packet, the first packet waits in the input virtual channel (buffer). Once, the occupied channel is released by the other packet, the first packet again participates in the arbitration and is routed along the requested channel, if wins in arbitration.

Thus, the role of an arbiter is similar to a referee who resolves the contentions among several packets requesting the same output channel in a router. The NoC routers implement various arbitration policies such as flit-by-flit rotating, contention-aware, priority-based, round-robin, first-come first-serve, etc.

4. Crossbar: The Crossbar unit is responsible for interconnecting the input ports to the output ports of the router. The arbitration unit controls the output data of the crossbar. All possible input data lines are linked with the input ports of the crossbar.

5. Link Controllers: The Link Controllers are responsible for the movement of packets through the physical channel which interconnects the input and output ports of adjacent routers. This data transmission control is required to prevent incorrect data replications and data overflow. The link controllers coordinate the transmission units of flow control on either side of a physical link. Existing control techniques like stop-and-go and credit-based are generally implemented for this unit. This unit is also responsible for implementing data synchronization interfaces to synchronize correct data transfer from one router to other. The NoC routers implement various flow control policies such as pipelined repeater-based, asynchronous queue-based, mesochronous, source-synchronous, etc.

#### 2.4 Switching Methods

A switching method is responsible for the effective management of network resources. The buffers and channels are counted as the main resources of an interconnection network. The switching method determines when and how a packet (or message) header is allocated the network resources during its travel along the route. One can also view the switching method that determines the connection of an input channel to an output channel. A good switching mechanism allocates the network resources efficiently so that the packets are delivered to their destinations with low latency and high throughput by efficient sharing of channels and buffer among them.

Flow-control methods are tightly coupled with buffer allocation and switching methods. The flow-control methods establish the connection between adjacent routes. They control the flow of the information by stopping and allowing it. When a packet is stopped, it needs some buffer area to get stored. If the flowcontrol method finds that the available buffer space is not enough to store the information, it stops the flow. As soon as, it detects the availability of the buffer space, it again starts the information transmission. In the absence of flow control mechanism, the packets may get dropped. On-chip router architecture depends on the selection of the switching method. The switching method also defines the services provided by the network. In this section, we brief about commonly used switching methods such as circuit switching, storeand-forward, virtual cut-through and wormhole.

#### 2.4.1 Circuit Switching

We begin our discussion with the circuit-switching method that works at coarsest granularity level and generally uses bufferless flow control. In circuit switching, prior to the transmission of data, the entire route (circuit) is first reserved. A packet header containing the destination address together with some control data is injected into the network. As the packet header advances towards the destination in the network, it reserves the required resources along the route. If the header is unable to acquire the required resource immediately at an intermediate router, it has to wait for the resource till being released. Once the header reaches the destination, an acknowledgment is sent back to source router indicating that the entire route followed by the header is setup. As soon as, acknowledgment packet reaches the source router, the source can then start the transmission of data packets over the reserved path. Once all data packets are sent, a control packet is transmitted in the network to terminate the connection circuit.

The circuit switching technique is generally employed for providing guaranteedthroughput and/or guaranteed-bandwidth in data transfer. In high-performance computing domain, Intel iPSC/2 [80] has used circuit switching technique in parallel machines. These machines use a Direct Connect Communications Technology. Another example that uses circuit switching is Motorola-based BBN GP 1000 [7]. This machine deploys butterfly topology: a multistage connection network. In on-chip networks, the circuit switching techniques is used to provide quality of service. Æthereal [87], MANGO [6], PNoC [52], DSPIN [83] are a few on-chip network proposals which use the circuit switching technique.

The main advantage of circuit switching is that it can transmit the data at full hardware bandwidth. It is useful for long and infrequent messages. However, it may block other messages, because, it reserves the entire route during the transmission of a particular message. Thus, this switching mechanism is inefficient as it wastes expensive channel-bandwidth in order to save relatively inexpensive buffer space.

#### 2.4.2 Store-and-Forward Switching

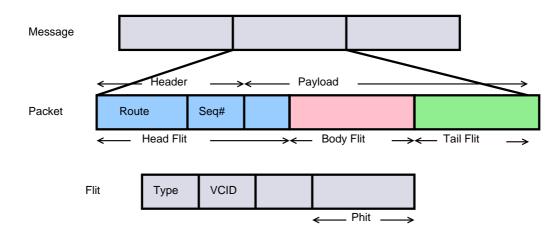

In circuit switching, once the path is reserved, the entire message is sent along the circuit till the transmission ends. Alternatively, before injecting the message into the network, it is divided into small fixed-length units called packets as shown in Figure 2.12. Each packet can be further divided into a number of flow control unit(s) called flit(s). There are three types of flits: Head flits, Body flits, and Tail flits. The first flit of each packet contains control and routing information, some data (optional) and is called head flit. Body flits contain the data. Tail flit contains some data (optional), and control information that shows that this flit is last flit for a particular packet. Flits can be further segmented into phits that represent the width of the channel. This switching method is called packet switching. The routing algorithm computes the route for each packet and forwards the packet individually from the source to the destination.

Figure 2.12: Message Composition

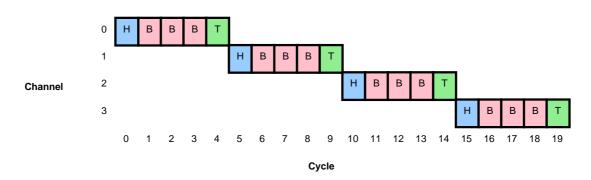

The store-and-forward switching is a kind of packet switching technique in which each router is provided with a buffer space equal to the size of the packet so that it can hold a packet completely. Before forwarding the packet to the neighboring router, the packet is stored at each intermediate router. Since every packet is first stored and then forwarded to the next hop, this switching is called storeand-forward switching. Figure 2.13 depicts the time-space diagram for store-andforward switching. A packet consisting of five flits is routed with no contention assumption. The path length is four hop. Before moving to the next channel, the complete packet is routed along one channel at each step of routing.

The store-and-forward technique is the first switching that has been used in many

Figure 2.13: Timing diagram for store-and-forward switching

parallel machines. The Manchester Dynamic Dataflow computer [50], the MIT Tagged Token Dataflow system [79] and the Denelcor HEPmachine are the few examples of earlier parallel systems that have deployed store-and-forward switching technique. Similar to the off-chip network field, Arteris [74], CLICHE [67], MicroNet [99], MESCAL [93], Nostrum [76] and Proteo [94, 89] form a short list of early NoC proposals that have used store-and-forward switching technique.

The store-and-forward is preferred when packets are frequent and short. This technique fully utilizes the communication channel when there is data to be sent, unlike circuit switching, where a set of reserved channels may be idle for a substantial period. In this switching, several packets of the same message can travel simultaneously in the network without waiting for the acknowledgment of first packet. However, dividing a message into the number of packets results in delay. Moreover, this switching needs additional time to assemble the packets into the original message at the destination. As the route computation is done at every intermediate router, it also causes overhead.

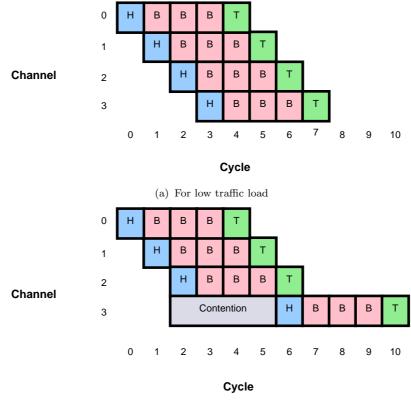

#### 2.4.3 Virtual Cut-Through Switching

In store-and-forward switching technique, a packet must be entirely buffered before it can move to the next hop. Thus, each router experiences serialization latency that results in high average network latency. The virtual cut-through switching is an improvement over the store-and-forward that tries to reduce the serialization delay required to buffer the complete packet at each router. It allows the packet to move to the next hop router soon after the routing decision is made for the packet header, if the next router is having enough buffer space needed to store the packet header at least. Thus, in this switching, it is not required to buffer the complete packet at the current intermediate router and can be cut through to the next router. The packet can be effectively pipelined via consecutive routers. However, when the packet header is blocked at an engaged router, it is buffered at that router. Therefore, virtual cut-through switching works as store-and-forward switching at high traffic loads.

Figure 2.14 depicts the time-space diagram for virtual cut-through switching. A packet consisting of five flits is routed with no contention assumption (Figure 2.14(a)) and with contention assumption(Figure 2.14(b)). Once any of the flits of the packet is arrived at the router, it is transmitted to next hop router if channel and buffer space is available at neighboring router.

(b) For high traffic load

Figure 2.14: Timing diagram for virtual cut-through switching

The virtual cut-through and store-and-forward techniques are packet-based techniques and thus has one main drawback. The buffer allocation must be in units of packets that makes these switching techniques very inefficient in terms of the buffer area. In the next Section, we have discussed an effective use of buffer space where the allocation of buffer space is performed in units of flits.

The router of Alpha 21364 [77] system and Chaos Router [65] are the examples that have used virtual cut-through switching technique. On-chip network proposals

such as IMEC NoC [3] and SPIN [49] have also used the virtual cut-through switching technique.

#### 2.4.4 Wormhole Switching

The major shortcoming associated with packet switching is that the buffer size must be at least of the packet size that makes the design of fast and compact on-chip router difficult. The wormhole switching operates in a similar way like virtual cut-through with one difference. It reduces the buffer requirement of the router significantly as the buffer space is allocated in units of flits. The buffer of wormhole router can be set as small as possible which reduces the hardware cost. A packet like a worm may spread over several channels (holes in the ground) during its flow. Thus, this switching is referred as wormhole switching. Other packets will not be able to reserve the channels that are occupied by a particular packet. The wormhole switching is preferred in the modern NoC-based systems like Teraflops [98], TRIPS [48] and Tile64 [4].

The interconnection networks researchers have presented some hybrid switching mechanisms such as buffered wormhole switching (BWS) [1] and pipelined circuit switching (PCS) [44]. BWS is a variation of the wormhole switching, and it combines the wormhole switching and packet switching aspects. The BWS was firstly presented and used in IBM Power Parallel SP2 [51]. PCS is a combination of the features of circuit and wormhole switching methods. The other switching techniques include Scouting switching [21, 25] and Mad Postman switching [59]. The scouting switching is introduced to enhance the capability of PCS technique to handle faulty channels. It also improves the performance of PCS technique.

## 2.5 Routing Algorithms

After topology selection, next logical step is the selection of a particular routing algorithm. A routing algorithm is responsible for computing the path that a packet should follow from the source node to the destination node. In this section, we introduce concepts and background of various routing strategies. As mentioned earlier in the Section 2.2, the selection of a specific routing scheme generally depends on the underlying network topology. We have presented routing concepts and background needed for the mesh-based network only as this thesis proposes routing algorithms for mesh networks.

#### 2.5.1 Deadlocks in Routing

The major issue related to every routing strategy is deadlock-freedom. A deadlock is a situation in which some packets cannot proceed further toward their destination as the resources (channels) requested by them are occupied by some other packets. In a deadlocked configuration, all packets are waiting for each other in a cyclic manner to release the resources, thus blocked forever. However, it is possible that a packet is permanently blocked in the network because the destination node does not consume it. This category of deadlock is produced at the application level, and we have not considered this type of deadlock in our thesis and thus, is beyond the scope of this thesis.

Figure 2.15: Deadlock configuration

The existing routing algorithms utilize either deadlock avoidance or deadlock recovery to achieve freedom from deadlocks. In deadlock avoidance strategies, some constraints are imposed on the routing algorithm such that deadlock can never occur. On the other hand, deadlock recovery strategies do not force any constraint on routing functions, thus allow deadlock to occur. These strategies need a method first to detect and then resolve deadlock configuration. If the deadlock is detected, some channels are deallocated (packets holding those channels are generally aborted) to resolve the deadlock. These schemes are useful only when deadlocks rarely occur [26]. Otherwise, the overhead produced by deadlock detection and buffer releasing would degrade the network performance considerably.

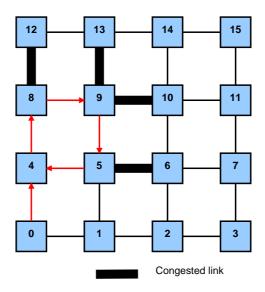

Figure 2.15 illustrates an example of deadlock configuration. This deadlock configuration is formed because four packets (p1, p2, p3 and p4) are involved in cyclic wait forever. At node 1, a packet p1 is coming from East direction and occupies the channel  $a_1$  for the destination node 3. This packet p1 is waiting for the channels  $b_1$  that is occupied by the packet p2. The packet p2 is coming from the North direction and has node 4 as its destination. Similarly, channels  $c_1$  and  $d_1$  are occupied by the packets p3 and p4, respectively. Packets p3 and p4 are coming from the West and South directions, respectively and have node 1 and node 2 as their destinations, respectively. All the packets are involved in cyclic wait and cannot advance further.

The deadlock configuration has formed because there exist cyclic dependencies among channels  $a_1$ ,  $b_1$ ,  $c_1$  and  $d_1$ . The packets are allowed to take any turn either clockwise or anti-clockwise. This cyclic dependency can be eliminated if packets are not allowed to take one turn (called prohibited turn) in each of clockwise or anti-clockwise cycle. The prohibited turns remove one dependency from each of the cycles, thus avoids the deadlock configuration. We have discussed routing schemes derived from the prohibition turns (simply turn model) in section 2.6. In another type of routing (deflection routing), deadlock-freedom is achieved using the idea that no. of input channels must be equal to the no. of output channels. Therefore a incoming packet will always has free output channel. In deflection routing, no network deadlock is possible [81], as all incoming flits are always routed outside of the router, without having to check in advance that the neighbor router has buffer space.

#### 2.5.2 Livelocks in Routing

Livelock is a situation where a packet never reaches its destination. However, it is possible that packets are not in a deadlock configuration, and they may be

Figure 2.16: An example of livelock